**AUGUST 2020**

l·Connect<mark>007</mark>

# DESIGNOTAL SERVICE OF THE PROPERTY OF THE PROP

# OUR LIBRARY IS ALWAYS OPEN

Registered members of my I-Connect007 have 24/7 access to our ever-growing library of eBooks, which now includes a wide range of topics from DFM to complex PCBs.

Enrich your mind and expand your knowledge! Download these popular titles with just a click.

They're pretty awesome!

"Mark does an outstanding job detailing what needs to be included in the handoff from designer to fabricator. This book should be required reading for every designer."

Douglas Brooks, Ph.D. BS/MS EE

Most of the design data packages that a fabricator receives contain inaccurate or incomplete data.

Don't be a data violator!

I-007eBooks.com/data

# DESIGNOT NO E

## **Fabrication Notes**

Do you hand off perfect fab notes to your fabricator? If this month's content is any indication, the answer is likely, "No." But this isn't about designers handing off bad data; the problem goes much deeper than that. This month, we decipher the process of creating fab notes, define what should and should not go into a design data package, and discuss what can be done to eliminate that dreaded afternoon phone call.

#### **FEATURES**:

12 Deciphering Fab Notes

Interview with Dana Korf

and Kelly Dack

26 Mark Thompson's Most Wanted: Accurate and Complete Fab Notes Interview with Mark Thompson

42 Dear Designers:

Please Include a Sanity Check

Interview with Rick Almeida

and Ray Fugitt

#### **FEATURES:**

Monsoon Solutions: Creating the Perfect Fab Notes

Interview with Jennifer Kolar and Dan Warren

The Role of EDA Tools in Creating Fab Notes

Interview with

Patrick McGoff

FEATURE COLUMN:

Erroneous Fab Notes:

Don't Blame the Designer

by Andy Shaughnessy

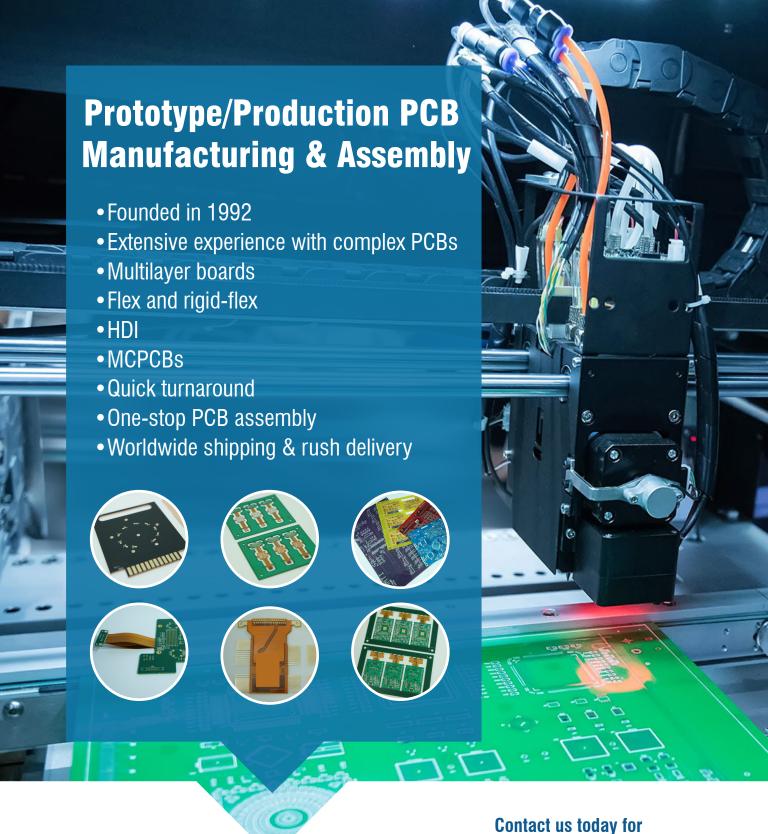

+1-437-987-6541 shinyipcbtaiwan@gmail.com

a speedy quote!

# DESIGNO07

#### **SHORTS:**

- 11 Secretary Elaine Chao Unveils

Guidance Document for Regulation

of Hyperloop

- 25 Solaris Acquires Jetbrain to Aid in Using Robots to Fight COVID

- 49 NI, Eta Wireless Accelerate Wideband Digital Envelope Tracking

- 57 SparkFun, Alchitry Bring FPGA Hardware and Software to Electronics Enthusiasts

- 65 Sondrel Looking for Electronic Designers to Become Chip Architects

- 88 Tianma Orders Keteeva Yieldjet Inkjet Printing System for OLED Display R&D

#### **DEPARTMENTS:**

- 113 Career Opportunities

- **122** Educational Resource Center

- 123 Advertiser Index & Masthead

#### **INTERVIEW:**

66 Things Designers Can't Unsee Interview with Kelly Dack

#### **COLUMNS:**

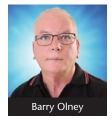

20 The Wavelength of Electromagnetic Energy by Barry Olney

- 34 Be Aware of Default Values in Circuit Simulators

by Istvan Novak

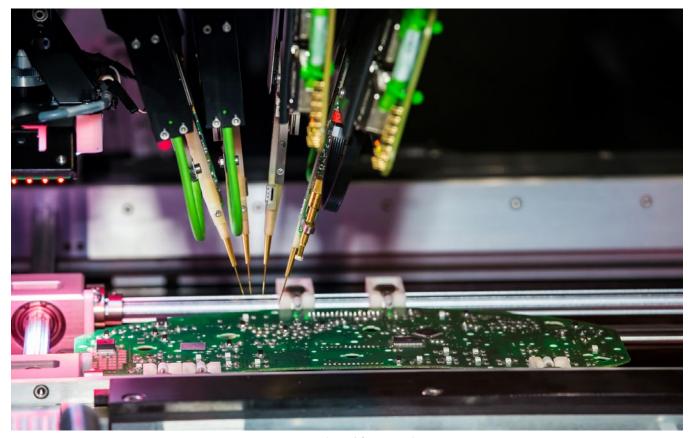

- 58 The Nuts and Bolts of Electrical Testing by Bob Tise and Matt Stevenson

- 76 How to Overcome Conformal Coating Challenges

by Phil Kinner

- 80 An Update on the Italian IPC Design Chapter by Patrick Crawford

- 84 It's Official: 1,000+ PCEA Members Worldwide by Kelly Dack

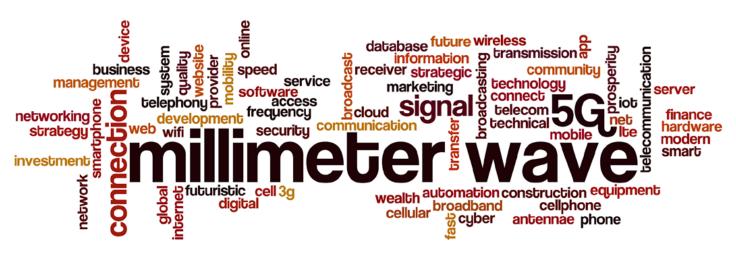

- 90 Utilizing mmWave Technology to Optimize High-Speed Designs by John Coonrod

#### **HIGHLIGHTS:**

**75** PCB007

HEI Þ

WANTER

- 93 MilAero007

- **110** Top 10 PCBDesign007

## Driving advances in automotive performance

The Automotive industry is held to the highest standards by consumers and the highly competitive market alike; both of which expect constant innovation in safety and performance.

In todays' world innovation mostly comes through the advancement of electronic systems, which are critical to the smooth and safe operation of any vehicle. From interior switches and under-the-hood controls right through to exterior lighting and sensor systems, we develop innovative solutions that enhance performance, providing the 'complete solution' at all levels.

We work to the qualified standards of the world's most renowned automotive manufacturers, providing electrochemical solutions that not just meet, but constantly exceed expected standards.

The combination of our 70+ years' experience in producing performance enhancing electrochemical solutions, together with our high standards of customer service and global reach really begs the question...

Isn't it time you discovered how Electrolube can serve you?

Scan the code to discover our full spectrum of electro-chemical solutions.

Tel: 800-474-1472 www.electrolube.org

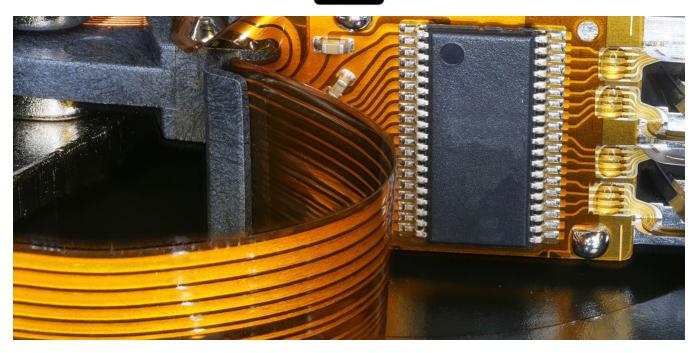

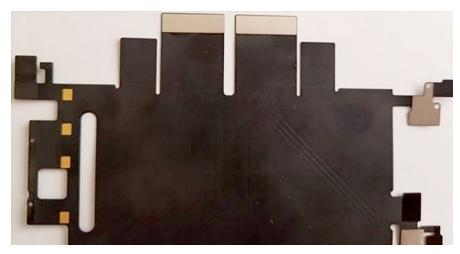

# FLEXOOT This Month in Flex

Getting your fab notes correct and complete can be challenging enough, but the task is amplified for flexible circuit designers, who must convey 3D flex design intent to the manufacturer. Communication is king here, and accurate fab notes are the currency of the realm.

FLEXOO7 ARTICLES:

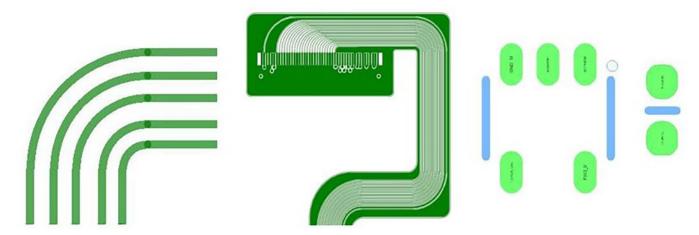

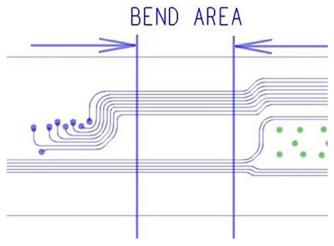

98 Flexible Circuit Design Rules for Beginners

by Olga Scheglov

**FLEX007 COLUMNS:**

**94** The Black Magic in the Business by Tara Dunn

106 Next-Generation Flex Circuits:

Monocoque Printed Circuits

by Dominique K. Numakura

**HIGHLIGHTS:**

105 Flex007

**FLEXOO7 SHORTS:**

104 TNO at Holst Centre Taking

Significant Steps Toward Enabling

3D Printing for Electronics

108 EHang to Expand Production Facility for Autonomous Aerial Vehicles

# Everyone in the industry should get their hands on this book.

A "must-have" for PCB designers, OEMs and fabricators, this free e-Book explains very complicated technology in a way that is easy to understand.

# Erroneous Fab Notes: Don't Blame the Designer

## The Shaughnessy Report by Andy Shaughnessy, I-CONNECTOO7

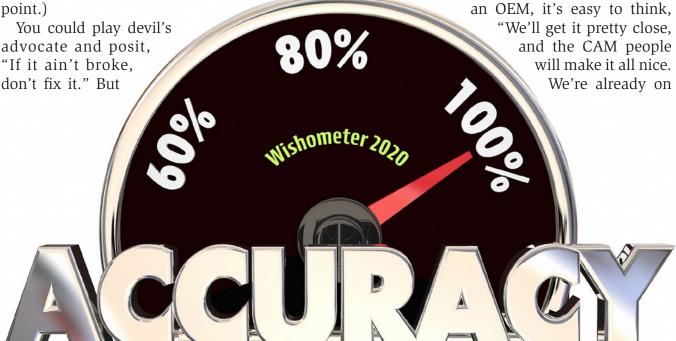

Do you hand off perfect fab notes to your fabricator? If this month's content is any indication, the answer is likely, "No." And you may not even know that your fab notes are incomplete or incorrect because your CAM engineers have been fixing your data for so long that it's become part of their job description.

But this isn't about designers handing off bad data; the problem goes much deeper than that. In fact, we really can't blame designers for a situation that they didn't create.

The system has enabled designers to continue sending out less than perfect fab notes—in effect, making the board shop's CAM department the final step in the design process. Some CAM engineers spend eight hours tweaking one data package, often before the fabricator even gets the job. (The CAM department is actually working in sales at that point.)

there are consequences for the OEM that hands off imperfect data, including time to market (which equals lost revenue) and weekend calls from the CAM department. But these ramifications are all "baked in the cake" at this point, and the actors seem to have accepted their roles.

What exactly does a fabricator need from a designer in the first place? We posited that question to Dana Korf, formerly the chief PCB technologist at Huawei. He answered, "Give me all of the data I need to build the board right the first time. Don't tell me how to do it; tell me what you need."

That clearly isn't happening very often. Some fabricators say that 90% of all new customers hand off inaccurate or missing data. But the CAM department's data-tweaking services make that fabricator an attractive supplier. If you're a CAD manager at

to the next design now, so don't bother me. Build the board."

Fabricators are caught in the middle. But what if fabricators started offering incentives for jobs that arrived with perfect data packages? The small- and medium-sized OEMs, especially startups, might just jump at such an offer. If board shops monetized the documentation process, I bet we'd see the percentages of imperfect data start to trend downward.

This month, we shine a light on the process of creating fab notes, define what should and should not go into a design data package, and what—if anything—can be done to eliminate that 5:30 p.m. call to the OEM on Friday night. We start with a conversation with columnists Dana Korf and Kelly Dack, who delve into the challenges of creating accurate fab notes, and the need to include all of the relevant data. Veteran CAD man Mark Thompson explains how easy it is to get design data right—and wrong and he shares some of his tips for creating great fab notes. Rick Almeida and Ray Fugitt of Down-Stream Technologies address what happens to incorrect fab notes in the CAD department, the role EDA tools can play in this situation, and how the current system enables designers to continue to keep handing off erroneous data.

Next, Jennifer Kolar and Dan Warren of Monsoon Solutions discuss the importance of communicating with your fabricators and why they almost never get calls from a CAM department regarding their documentation. Patrick McGoff of Mentor, a Siemens Business, offers advice to new designers facing fab notes challenges and explains how intelligent file formats like ODB++ help eliminate miscues during the data handoff process. Tara Dunn illustrates how flex fab notes differ from their rigid PCB brethren, as well as how the 3D structure of flex presents even more data challenges.

We also bring you columns from Barry Olney, Istvan Novak, Kelly Dack, Patrick Crawford, Phil Kinner, John Coonrod, Matt Stevenson and Bob Tise, and Dominique Numakura. We also have a great article by Olga Scheglov, CID+, on design rules for new flex designers.

There's still a lot of craziness going on in the world right now, but we continue to see amazing examples of innovation in this industry. When COVID-19 is a thing of the past, this industry is going to blast off. The only question is, "When?" See you next month. **DESIGNOO7**

Andy Shaughnessy is managing editor of *Design007 Magazine*. He has been covering PCB design for 20 years. He can be reached by clicking here.

#### **Secretary Elaine Chao Unveils Guidance Document for Regulation of Hyperloop**

U.S. Department of Transportation Secretary Elaine Chao and the Non-Traditional and Emerging Transportation Technology (NETT) Council unveiled the guidance document on a clear regulatory framework for hyperloop in the United States.

"This guidance bridges the gap between innovator and regulator, prioritizes safety during development without hampering innovation, and promotes mutual awareness between industry and government," said Chao.

The regulatory guidance document for hyperloop is the first of its kind in the world, further proving that the US intends to be the leader in the industry.

"Secretary Chao and the NETT Council are working at an unprecedented speed

to ensure that the United States is at the forefront of hyperloop development," said Jay Walder, CEO of Virgin Hyperloop. "It's clear that the USDOT shares our vision for infrastructure development as a way for the country to not just rebuild, but evolve as we emerge from this crisis."

As an entirely new category of transportation, hyperloop will unlock exponential growth opportunities for cross-industry manufacturing and development jobs, across construction, aerospace, rail, automo-

tive, aviation, electric vehicles, and autonomous control. Last month, Virgin Hyperloop announced a partnership with Spirit AeroSystems, one of the world's largest aerospace manufacturers.

(Source: Globe Newswire)

## **Deciphering Fab Notes**

#### Feature Interview by the I-Connect007 Editorial Team

When we started planning this issue on fab notes, we knew we'd have to speak with Dana Korf and Kelly Dack. Dana is the former chief PCB technologist for Huawei and a front-end director for PCB board manufacturers, such as Multek, Sanmina, HADCO and Zycon. Dana has made a point of working with designers and helping them provide accurate fab notes and documentation each time. Kelly Dack has been dealing with (and correcting) errorfilled and incomplete fab notes for years. In this wide-ranging discussion, Dana and Kelly explain some of the challenges they encounter with fab notes, and what designers can do to create better documents and head off that dreaded phone call at 5:30 p.m. Friday.

**Andy Shaughnessy:** Dana, why don't you give us an overview of what manufacturing notes are and their main function in the design process.

**Dana Korf:** When we talk about fab notes, to me, the fab print is the main document, along with

the graphical data, which has critical information like the stackup, drill tables, some dimensioning and tolerancing, and then—down the left-hand side—a series of notes where people talk about a lot of things. The fab notes will reference materials, solder mask type, laminate types, copper maybe, reference off their acceptability specs, and then some miscellaneous comments about the design—all telling the fabricator or assembler what to do or not to do.

**Shaughnessy:** They all fit under the umbrella term of manufacturing notes, correct?

**Korf:** I'd say most of the notes are manufacturing-related. "Here's what to do or not to do." Very rarely do you get design-related notes. Probably the most common ones I've seen are around signal integrity. "I want this Dk at 8 gigahertz." That's more design-related because you don't test it at 8 gigahertz. Typically speaking, they're more related to manufacturing or what I call acceptability.

WE MIGHT NOT DATE BACK TO THE RENAISSANCE BUT BROKERING PCB SINCE 1971 IS QUITE IMPRESSIVE AS WELL?

#talktothePCBexperts

**ELMATICA®**

**Shaughnessy:** Kelly, on your side, you've been dealing with a lot of these manufacturing notes. Tell us about your engagement with manufacturing notes and some of the issues that you've seen.

**Kelly Dack:** It's a pleasure to speak with Dana. I think it's good to clarify that notes are meant to specify or define what a designer wants in a bare PCB. As we go through a list of notes, we need to be able to communicate and define

Kelly Dack

and specify the bare board in order to end up with what we want.

For instance, a board outline can be manufactured in several different ways. We don't necessarily need manufacturing note to tell the board shop that the edges of the board shall be routed unless it really matters in the rest of the design or that the

board edges shall be V-scored. We do better by defining the board outline and tolerance, letting that stand as the specification, and allowing the manufacturer to deliver the specification.

Korf: I agree. As I tell people, "Tell me what you want, not how you want me to do it. I won't tell you how to design the board, and vou don't tell me how to build a board." The most common problem I see in notes is that, a lot of times, the designer cut and paste from other boards, and they may not make sense. Or you have new designers who aren't familiar with the specs. My favorite one is, "This board shall meet IPC Class 3 requirements," yet the annular ring doesn't. You have to go back and say, "Your board doesn't meet Class 3, and I can't get there with this design. What do you want me to do?" You hear back, "Well, make it Class 2."

**Dack:** I can totally relate. Working for an EMS, I see a myriad of notes that just don't make sense. Sometimes, we can tell that they've been cut and pasted, and the designer has no clue about what they are inflicting on the bare board manufacturer. I just had a scenario where a board requirement came in. The material was FR-4, and there were not too many notes. Our job as an EMS provider is to get this board quoted at several board shops with which we have relationships. We're going to get numbers based on what the bare board shop says they can do. Believe me, their job is to win the quote, and they're not going to do it by quoting the highest-rate materials or the highest Tg materials. They're going to presume that they can use the lowest-rated materials.

We had a board that was quoted at 130 Tg material, but it needed to be changed to 170 Tg because of all the different thermal excursions that it would be going through in assembly. A high-temp material would have been a better choice, but because it wasn't specified, we ended up wasting a lot of people's time. Actually, the designer, through his lack of specification skills, ended up wasting a lot of people's time.

**Korf:** Back when high-end boards were U.S.-centric or European-centric, the fabricator wasn't as cost-sensitive. The fabricator would pick a material beyond maybe what the designer wanted because we knew better. It would probably last better or perform better. Then when we started shifting to Asia, they did exactly what you said. You said FR-4, they quoted standard Tg FR-4, and they always came in cheaper. We had to kind of retrain everyone to say, "Give them what they say, because that's the world now. Don't give them more than they're willing to pay for."

We had a great example in China a couple of years ago. A company came in and just said FR-4, so we put in a halogen-free mid-Tg material, and we built the prototypes in a couple of cycles. It went just fine. We got it quoted. Correction quotes went out, and everyone was happy. Then, the final drawing came in, and it said, "We want high-Tg FR-4." "But that's not what you said on the prior two revisions." Everyone freaked out. "It's the fabricator's fault."

What do you mean it's our fault? The person said FR-4, so we picked one. Actually, we probably picked not what we thought the design actually wanted, but what the cheapest one was. As we always say, it's always the fabricator's fault. Front-end people know that board shops and front-end engineers are always at fault for everything because they give us the most money and computers and higher-paid people, so we should never make mistakes. That's kind of normal.

Another famous one we see all the time is when you get a drawing that says, "ITAR restricted." I'm looking at it in Asia. I'm going, "This says ITAR. We're not supposed to see it." "Well, you're American." No, I can't see this in China. It's supposed to stay in the U.S."

We go back to the customer, who says, "That's our commercial division." Well, your note says it's ITAR. We can't quote it. They respond, "It's okay." No, it's not okay. I can't take a verbal waiver for this. People, particularly purchasing agents, don't read the notes, number one. They don't necessarily understand what it means. I've seen that multiple times.

Dack: Usually, board manufacturers will not complain or raise questions until after winning the quote. That makes specification even more important. The less you specify, the more the supplier can agree that they can deliver until the time that they win the quote. That is when we typically see the questions roll out, and it's just a show-stopper.

**Barry Matties:** Do you see that prices tend to be revised at that point as well? Do you ever see an increase?

**Dack:** Yes. This causes a tremendous problem. For instance, in our EMS world, we negotiate with our customers because we have to deliver a quotation for the work also. Our quotation is based on quotations from other suppliers. In the case of a bare board, our job is determining a price, and our costs rely heavily upon the quotations that we receive from our suppliers. If we don't get an accurate quote due

to lack of specification, then we have to subject the customer to a change in price after we have quoted the work. When prices change, it's never pretty.

**Korf:** I'll kind of agree and disagree with Kelly on one point. I agree that a lot of quotes come in, and you don't do DFM reviews during a quote typically because it takes a lot of work, but at most front-ends in large volume shops, 25–50% or more of their capacity is taken on

pre-design DFMs. You get a design that comes in, and prior to quoting, the sales folks say, "We need a full DFM." You do a full DFM, all the TOs, stackups, and everything and send it back. It's actually quite a significant portion of the capacity. You would always try to argue, "We shouldn't be doing DFMs for people unless

Dana Korf

we have a high probability we're going to get the order." I used to actually track that. I used to track DFMs per part number per customer to feed back to sales and say, "I had one customer one time. We did 11 DFMs for five part numbers and never got an order, and somebody else got a really nice design package to build."

**Dack:** To add insult to injury in this industry, unless the customer has requested the DFM analysis, which good customers do, customers that have a lack of specification don't want to hear about all the problems with their product. Could it be that suppliers are concerned about losing the quote and therefore keep questions close to their chest until winning the quote?

**Korf:** There are two answers to that. At some OEMs, the designers want to know all of the issues, and they get mad if you don't ask all the questions. There are other ones that never want to hear a question. It's part of the psychology of front-end engineering. You catego-

rize people that way. "These people want to hear, but these people don't." The ones that don't want to hear issues, you just give them the ones that make it totally unmanufacturable. Just say, "We have to stop." I call it "law of physics"-type questions. It can't be built unless we resolve the issues. Definitely, in a competitive bidding situation, there are a lot of EMS providers and a lot of people that are buying the boards for assembly that would just be price-based. They don't care. It's just price. If you're the cheapest, you get the order.

Companies will learn those customers, too, and tailor their responses to them. There may be a partial high-level DFM being done in the background. We look for any major issues that may cause a yield hit, a rework hit, or a

major cost hit. Sometimes, it's done in the quoting group, sometimes by another group.

**Dack:** I think it's very valuable to establish the orientation of the documentation. We start every note set with the primary side of the board shown, and we follow the IPC standard declaration of a primary side and a secondary side. The interpretation of that is that the primary side is the side that the designer has designated.

It got confusing. We all know the story of how the solder side of the board became the solder side, and the component side became the component side. With complex boards now, it's not as clear. Where we have gone is that the primary side is the side that the designer has designated as such.

**Korf:** That note's real critical for assembly. For fab, we're going to look at a file that says the layer names. What's the file layer name, and how do I match that to the board? The primary side, is it called layer 1? Is it called top? Is it

called Jim? I don't really care what it's called. Just tell me what it is. Most fabricators will align boards the way they want to build them. They might not label them the same way as the designer, just to have some standardization in the factory. From a conversation standpoint, it's always good for assembly. For fab, it's not too useful. We just care about matching the data layer names to the actual data provided.

**Dack:** In the context of the design, if you're going to specify Class 2, you'd better be designing Class 2 and not a different class for manufacturing and inspection purposes. What do you think?

> Korf: That's critical because that guides a lot of default criteria, the IPC class in general. A lot of people will say, "I want Class 2, except for my plated through-holes. My annular ring will be Class 3." One of the consulting projects I've set up to solve someday is this:

category called AABUS, or "as agreed between user and supplier." If you look at IPC-6012E, there are 38 sections and tables that have that as a criteria. If everyone technically followed that spec, we would have to have 38 ques-

Every IPC spec has this

tions every time going back to the customer, saying, "What do you want to do?" No one does that in reality. That's one of the conflicts in the specs versus reality. No one is going to ask 38 questions every single time just because of the IPC spec, and the committee couldn't agree on an answer. Or, as I call it, some of these AABUS categories should be a tutorial. You should worry about this. I agree that the IPC class note and exceptions to it is critical.

Happy Holden: Dana's hitting all of the key points. The big problem I always have is the

difference between a quick turn local PC shop and high-volume offshore company in terms of the difference of materials and the pain that it caused depending on how sensitive the board is. I don't have any notes of any particular references other than, eventually, you'll get around to hole plugging, which has always been a headache from a notes point of view. I always tell people, "Just steal the picture out of the IPC standard and paste that on the drawing so that we can see what it is. Don't make up new words." Especially if you're going to go to Asia, I remind people that English is usually not their native language. A lot of these made-up words that we use to describe PCBs don't translate well into Chinese or other languages. It's a source of misunderstanding and error.

**Shaughnessy:** What do you think is one of the biggest mistakes that designers make, and what advice would you give for correcting them?

**Korf:** From a notes standpoint, one of the biggest reasons I hear for a mistake is that they just cut and pasted from another design. They didn't really read them. They may not really understand the meaning of the notes that they're using. That's probably the number one reason I hear for errors. There's no designer out there that I know of who intentionally designs a bad board. It's just that they don't realize it. You see a lot of ODM designers who are designing a cellphone one day. The next day, they're designing a medical device. They just have no experience. They don't really understand what notes should be or shouldn't be on a drawing. That's probably my number one reason.

**Holden:** One of my biggest issues is that a lot of times in Europe and the U.S., for simplicity, you standardize on a standard panel size. But in Asia, because the material is so much of the cost, they're a lot more sophisticated on panel size. Designers, if they know they're going to go offshore, don't find out really what the panel size is and what the border requirements for a preferred vendor or something like that are. You can easily, in choosing board sizes, screw up the cost because, with 1/4" less in some dimension, we could increase the panel array quantity, reducing the cost per board. Maybe Americans are willing to waste the laminate, but in Asia, they don't like to waste laminate.

**Korf:** That's very true. Also, we're still working in a 1980s Gerber-based world where we have just a plotter language telling you what line and circle to draw. I need a piece of paper to interpret these lines and circles. I'm very active in the IPC-2581 committee. If you look at having intelligent data where you can attribute everything, a lot of these notes actually disappear. Like materials, they disappear. You just include the material spec in your stackup data. You don't need a drawing. You don't need a note. There's a lot of notes you don't need telling you what to do because it's already in the data. That's part of the 10-year transition as we move away from Gerber-based data to intelligent data that we can start getting rid of some of these notes. A lot of times, these notes contradict with the picture on the drawing and/or the data. If it's included in the data from the CAD system, then we'll start to see the elimination of both the notes and some of the issues.

**Holden:** I can't figure out why Gerber still exists. Nothing else in electronics is 60 years old. If electronics are three years old, they're getting toward obsolescence, yet we're stuck.

**Korf:** ...on a plotter format from the 1960s. Exactly. One of the most common issues is that you get a board outline drawing on the fabrication print. You extract it from your data file, and they're different, or you get a netlist that doesn't match the data. I presented at IPC APEX EXPO a couple of years ago. I asked the audience, "When we ask the question, should we use the netlist extracted from the Gerber or the original netlist? What should we use?" Everyone responded, "Gerber," and then laughed. They all realized what a nonsensical answer it was.

**Matties:** Is there any sort of standard for creating fab notes, or is this really up to the designer to decide what you need to know?

**Korf:** A lot of board shops will give suggested standard notes to customers, but there are no standards in the industry that I'm aware of.

**Holden:** There will be with IPC-2581.

**Korf:** It will give you a way to transmit the data, not the actual note contents themselves.

Holden: Yes, but you have more descriptive descriptions. You also have a section of 2581 that includes notes.

**Korf:** Correct. You can embed it in the file.

Matties: But it's still discretionary as to what the exact notes are.

**Holden:** That's the whole thing about electronics and printed circuits: If you come up with a neat idea that nobody has ever thought of, and it involves PCB assembly, if you want the right product back, you'll have to describe it in the notes because it's not coming by any standard.

**Matties:** The designers realize that there are problems, and they're looking for answers. If you're looking for an answer, what is it, Dana?

**Korf:** I'm a simplistic person. My goal is to build whatever you send me without having to ask a question, and you get what you wanted. It sounds like a simple mission statement. The biggest issue is conflicts.

**Matties:** That puts the onus on the designer.

**Korf:** Yes. It puts it on the designer or whoever prepares the document package. Now that we have an EMS step in there, sometimes, it gets confused in there. They mix and match revisions together. I see that a lot, such as Rev B fab print with Rev C data. Someone will revise

a layer, so you'll have one layer of Rev D and everything else at Rev C, and it doesn't match all of a sudden. There are lots of reasons. As I tell the CAD system people, "None of your tools work." Talk to anyone in the world and say, "What percent of your data packages is coming clean that you don't have to clean up or have issues with?" Most people will say very few. It's a very small percentage.

**Matties:** If a designer is looking at the data set that they need, is the best course of action to first talk to the manufacturer?

**Korf:** From a design and capabilities standpoint, absolutely. The data required is the same for everybody. I doubt if there's any vendor-tovendor or region-to-region difference there. It just needs to match. The problem is, a lot of times the vendor isn't selected until the design is done. The designer hands it off to an EMS company, which then visits 12 people. They select two, and it's too late.

**Matties:** Are fab notes generated during the design process or post-design?

**Korf:** Probably both.

**Dack:** From the standpoint of the designer, the designers don't know what they don't know. They need to know what they don't know. The only people that are going to enlighten them are the stakeholders that they're working with. In this case, if it's a bare board, they need to engage the fabrication stakeholder or supplier to discuss topics of capability because without marking that line in the sand, they are not implementing DFM.

**Korf:** As a fabricator doing pre-design DFMs, I was always happy to do that if they would do what we asked, or we compromised on what would work for the design. Unfortunately, there's a lot, especially large companies, that have in their process, "I have to have two DFMs before I can release to manufacturing." They get the first prototype and test it. Then, you get the second revision of the board, and

it includes all of the same issues they had the first time. Next, you get the production board. All the issues are still there.

**Dack:** They want to manufacture for their design. It goes contrary to everything that we've been pushing for the last few decades with regard to design for manufacturability in other words, finding out what's available. This is not rocket science; these are standard, regular boards. There are proven capabilities out there that we need to design around if we expect that our board is going to go to market in the fastest time possible.

**Korf:** Also, some fabricators don't want to give out their rules because they think it's IP, and it really isn't. They're forcing bad designs to come in that they aren't capable of building because they refuse to tell them what their capability is. I put the fault on both hands there, not just always the designer.

Shaughnessy: If you have good communication between the designer and the fabricator, the designer gets to know your capabilities, and you know what to expect from the design team. It seems like that would be the key.

**Korf:** If the designer has five fabricators, all five

fabricators can agree on a common set. That's been done many times.

**Dack:** Yes. That gets back into the, "Well, the other people built it." That's problematic, too. It can go both ways. It was probably an onshore supplier for it to do anything because they're building three or four of them. When it turns into production, and they're building millions, things change a lot from a capability standpoint.

**Korf:** To wrap up on notes, when I was in Asia, my team would bring me a note and say, "What does this mean?" Think about it: You might have an engineer in France who speaks French and puts in a note in English, and I don't know if they've learned British English or other variations. It then goes to someone in China whose native language is not English. What English did they learn when they read the note? The problem with notes is that sometimes, it's not clear if you speak the native language what it is a person is asking. As Kelly just said, if you assume, you're going to assume wrong, and you're dead.

**Shaughnessy:** This has been great. Thanks for speaking with us.

Korf: Thank you, Andy. DESIGNOO7

### **Professionals Seeking Employment**

D.B. Management Group L.L.C. is currently working with a group of professionals who are seeking new positions.

## The Wavelength of **Electromagnetic Energy**

#### **Beyond Design**

by Barry Olney, IN-CIRCUIT DESIGN PTY LTD / AUSTRALIA

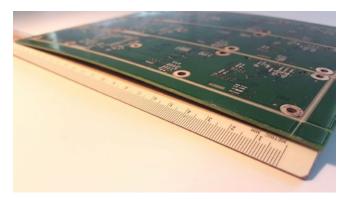

The speed of light is the one universal physical constant that we are yet to break. It is the limit of the velocity at which conventional matter and information can attain in our universe—without warping space-time, of course. At a lightning 299,792,458 m/s, it is the maximum speed at which massless particles (or waves) of light, electromagnetic energy, and gravitational waves travel in a vacuum. In this month's column, I will look at how to simply measure the speed of light and how the wavelength of electromagnetic energy relates to the multilayer PCB.

One morning recently, whilst eating my vegemite toast (as Australians do), I was reading my weekly New Scientist Magazine and came across an interesting article on how to measure the speed of light using a chocolate bar and a microwave oven. Here's how it works.

A microwave oven's magnetron (RF transmitter) oscillates at 2.45 GHz. Electromagnetic energy in this frequency range has an interesting property: It is absorbed by water, fats, and sugars. The microwaves, in the turned cavity, penetrate the food and excite the molecules heating the food throughout—provided the turntable is rotating. But for this exercise, the chocolate bar needs to be stationary, so remove the turntable.

Since the chocolate bar is not rotating, the microwaves are not evenly distributed throughout the bar, and regions of chocolate will begin to melt in the high-intensity areas. Chilling the bar first makes the molten areas more distinct. This will take approximately 50 seconds on high power. Take care not to exceed 60 seconds, or you may have a mess to clean (lick) up.

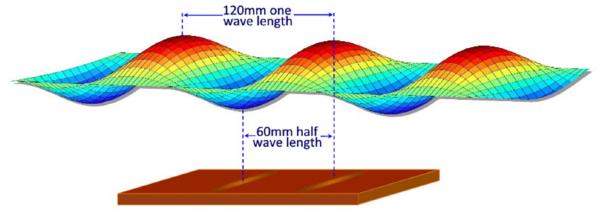

Figure 1: Half wavelength between hot spots. (Source: NASA Goddard Space Flight Center)

Electromagnetic energy travels in a wave through a vacuum or air at the speed of light. The distance between the peaks of the wave is the wavelength of the energy. As the wave travels, the peaks and troughs heat the chocolate. By measuring the distance between these hot spots, one can determine the half wavelength of the energy (Figure 1). You

should get about 60 mm between the melted globs. I got 58 mm after 45 seconds. However, there is plenty of leeway in the dubious accuracy of my plastic ruler and failing eyesight. Doubling this (120 mm) gives you the wavelength related to a frequency of 2.45 GHz. The following equation is used to calculate the velocity (v), where f is frequency and lambda  $(\lambda)$  is the wavelength.

#### Equation 1:

$$v = f\lambda$$

= 2.45GHz x 0.12m = 294,000,000 m/s

For an extremely rough measurement, this is very close to the actual velocity of light (299,792,458 m/s). Note that light will travel a little slower in the air than a perfect vacuum.

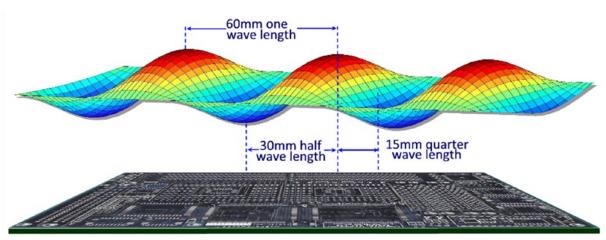

Now, let's look at how this relates to the speed of electromagnetic energy in multilayer PCBs. If you have a digital signal running at a clock rate of 2.45 GHz, then one would expect

the wavelength to be 120 mm. Wrong! Unfortunately, the relative permeability or dielectric constant (Dk) of the surrounding materials impacts the velocity of propagation at the speed of light (c).

$$v = f\lambda = \frac{c}{\sqrt{Dk}}$$

A vacuum has a Dk = 1, air = 1.0006 and typical FR-4 = 4. Then, solve Equation 2 for the wavelength, including the Dk of the dielectric material:

$$\lambda = \frac{c}{f \, x \, \sqrt{Dk}} = \frac{299,792,458}{2.45 \, \text{GHz} \, x \, \sqrt{4}} = 61 \, \text{mm}$$

Therefore, the FR-4 material in a stripline configuration slows the propagation speed and decreases the wavelength of the electromag-

Figure 1: Half wavelength between hot spots.

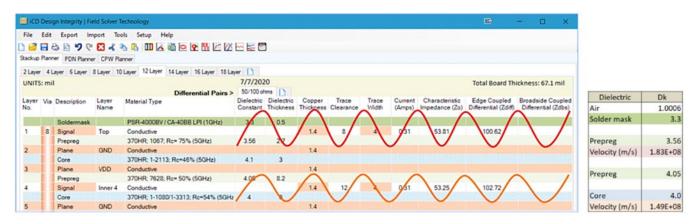

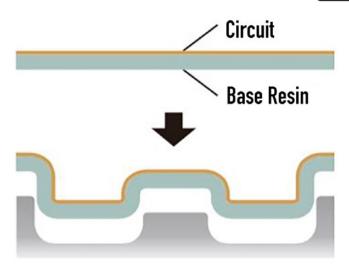

Figure 2: The wavelength of a 2.45-GHz signal on a PCB inner stripline layer.

Figure 3: Comparison of Dk per layer and relative velocity.

netic wave down by about half (Figure 2). But that all depends on the exact dielectric constant of the surrounding materials.

For the top layer 1, the electromagnetic energy travels in a combination of prepreg, solder mask, and air (Figure 3). The effective Dk will be around 2.68 with a propagation speed of 1.83 x 108 m/s. For layer 4, there is a combination of prepreg and core with an effective Dk of 4.03 and a speed of  $1.49 \times 10^8 \text{ m/s}$ . This should be simulated by a field solver, as it depends on the combination of materials and their Dks, order, and thickness. From this, one can see that the propagation speed of the electromagnetic energy is always faster on the outer microstrip layers than the inner stripline layers.

At high frequencies, short traces (particularly stubs or unterminated traces) on a PCB can act as a monopole or loop antenna. Differential-mode radiation is the electromagnetic radiation caused by currents consisting of harmonic frequency components flowing in a loop in the PCB. The radiation is proportional to the current loop area and the square of the frequency of the signal. Common-mode radiation is the electromagnetic radiation caused by current flowing in an unterminated trace (or terminated with a high-input impedance device) and may require load terminating resistors to eliminate reflections. The radiation resembles that of a monopole antenna, and the magnitude is proportional to the current per line length and frequency.

Trace antennas form a monopole with a quarter wavelength  $(\lambda/4)$  at the resonant frequency. Monopoles require a ground plane; this forms the other quarter wavelength to radiate efficiently, which is not desirable in this case. It functions as an open resonator, oscillating with standing waves along its length. The radiation pattern is practically omni-directional.

Unfortunately, the high-frequency components of the fundamental (lowest frequency in a complex wave) radiate more readily because their shorter wavelengths are comparable to trace lengths, which act as antennas. Consequently, although the amplitude of the harmonic frequency components decreases as the frequency increases, the radiated frequency varies depending on the characteristics of the antennas/traces.

At 2.45 GHz, an 18-mm trace on the outer, microstrip layers may radiate while on the inner stripline layers, 15 mm (600 mils) is sufficient. And as we increase the frequency to 10 GHz, the maximum length is just 3.75 mm (150 mils), which is incredibly short. Stripline traces are embedded between two planes, which dramatically reduces radiation with the exception of the fringing fields from the edge of the board. However, the outer microstrip layers will radiate; hence critical, high-speed traces should be avoided on these layers.

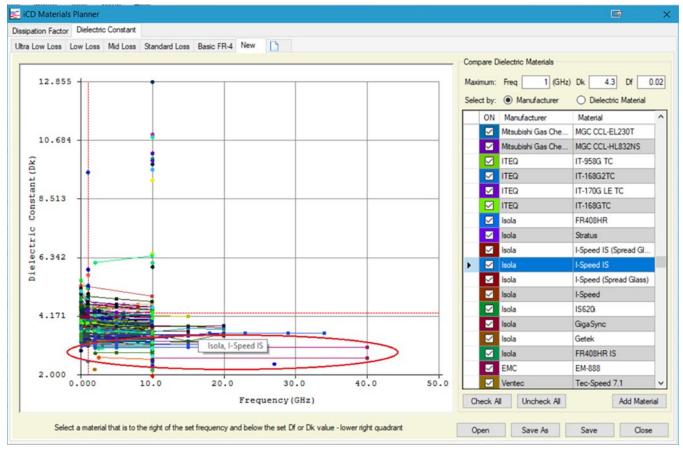

Since the wavelength of electromagnetic energy depends on the signal frequency and dielectric constant of the surrounding materials, a low Dk (circled in Figure 4) is preferred for high-speed design. Fortunately, low-loss materials generally have this characteristic.

Figure 4: Plot of dielectric constants of high-speed materials (iCD Materials Planner).

#### **Key Points**

- Microwave energy is absorbed by water, fats, and sugars.

- Electromagnetic energy travels in a wave through a vacuum or air at the speed of light.

- The distance between the peaks and troughs of the energy is a half wavelength.

- The dielectric constant of the surrounding materials impacts the velocity of propagation of the signal.

- The FR-4 material in a stripline configuration slows the propagation speed and decreases the wavelength of the electromagnetic wave down by about half.

- In a microstrip (outer layer), the electromagnetic energy travels in a combination of prepreg, solder mask, and air, which reduces the effective Dk.

- In a stripline, there is a combination of prepreg and core.

- The propagation speed of the electromagnetic energy is always faster on the outer microstrip layers than the inner stripline layers.

- At high frequencies, short traces (particularly stubs or unterminated traces) on a PCB can act as a monopole or loop antenna.

- Trace antennas form a monopole with a quarter wavelength  $(\lambda/4)$  at the resonant frequency.

- High-frequency components of the fundamental radiate more readily because their shorter wavelengths are comparable to trace lengths.

- Outer microstrip layers will radiate; hence critical, high-speed traces should be avoided on these layers.

- A low-Dk material is preferred for highspeed designs.

#### **Further Reading**

- Barry Olney, "EMC Design for High-Speed PCBs," Printed Circuit Design Magazine, 1996.

- New Scientist Magazine, Issue 3285, June 6, 2020

- Wikipedia, "Speed of light."

- Amit Bahl, "Signal speed and propagation delay in a PCB transmission line," June 19, 2018.

- Roshni Prasad, "PCB Trace vs. Chip Antenna Design Considerations," Abracon LLC.

Barry Olney is managing director of In-Circuit Design Pty Ltd (iCD), Australia, a PCB design service bureau that specializes in board-level simulation. The company developed the iCD Design Integrity software incorporat-

ing the iCD Stackup, PDN, and CPW Planner. The software can be downloaded at icd.com.au. To read past columns or contact Olney, click here.

#### **Solaris Acquires Jetbrain to Aid in Using Robots to Fight COVID**

Solaris Disinfection Inc., a leader in IoT-connected service robotics, whose flagship Lytbot automated disinfection system is currently being used by hospitals across North America in the battle against COVID-19, announces the acquisition of Jetbrain Robotics, an innovator in hospital logistics and patient experience using autonomous mobile robotics (AMR). Invested in and supported by world-class investors Brinc & Artesian Venture Partners (AVP), Jetbrain's technology improves operational workflows in complex healthcare environments, providing quantifiable efficiencies and patient experience improvements.

Since 2017, Solaris has conducted research on the

effectiveness of its pulsed UV technology against communicable human respiratory viruses like novel coronaviruses (COVID-19). "COVID has accelerated robotics deployment by five years," said Adam Steinhoff, Co-Founder, and CEO, Solaris. "In continuing our mission to improve the safety of patients and support healthcare workers, we identified Jetbrain's technology as an opportunity to improve upon our core products while providing safety, accountability and compliance-based platform technologies that help our customers effectively utilize resources and improve workflows."

Adds Val Ramanand, co-founder and executive chairman, Solaris, "At Solaris we are very proud of the growing impact we make on a daily basis in the healthcare industry by delivering practical and approachable products, designed to improve patient outcomes and healthcare operations. The acquisition of Jetbrain supports our continued mission

to improve care, keep spaces safe, and ultimately help save lives in healthcare facilities globally."

Jetbrain products include delivery robots that feature a secure and traceable chain of custody for medicines and blood products, as well as patient experience robots that provide anything from clinical support to wayfinding help. The addition of Jetbrain's team enhances Solaris's expertise in healthcare robotics while extending its offering from whole room disinfection to automated delivery, logistics, and ultimately patient experience, thus delivering industry's first ecosystem approach to healthcare robotics.

(Source: PR Newswire)

#### Feature Interview by the I-Connect007 **Editorial Team**

Editor's note: When this interview was conducted, Mark Thompson, CID+, was in engineering support at Prototron Circuits. Mark is now a senior PCB technologist with Monsoon Solutions, a design and engineering bureau in Bellevue, Washington.

In his position in the CAM department at Prototron Circuits, Mark Thompson has seen his fair share of puzzling data and documentation. He discusses some of the difficulties he's encountered with designers' fab notes and provides designers with a number of points to consider the next time they send out a design.

**Andy Shaughnessy:** Mark, give us a taste of some of the more common problems you see with customers' fab notes.

Mark Thompson: From where I sit as an engineer in a fabrication environment, the biggest thing I see is designers who produce boiler- plate notes that they get from their CAD system. A lot of them have templates that are already embedded in their system. They can just call it up and say, "Notes 1–14 are golden. We're going to put those on." Ultimately, if it doesn't have anything to do with the job, get rid of it because it's going to cause additional grief and phone calls from the fabricator.

There is some information that your fab notes should absolutely have, including standards, a board class, and material type. Flatness is another; if flatness is critical, put in tolerance for flatness. If it's a board that is massively dielectrically challenged, with very thin dielectrics on one side and very thick dielectrics on the opposing side, whether you add additional metal on the outside or one is a solid plane and one is a full signal, it can still end up with some modicum of warpage. Warpage being an issue, flatness is a callout that you're going to want to have in your drawing.

We also need hole tolerances, dielectric thicknesses, shape tolerances, and the overall board dimensions (is it 4" x 5"?), as well as surface finishes, immersion gold, immersion silver, deep gold, or HASL. All of the surface finishes have a tolerance and a thickness based on IPC standards that need to be adhered to. That's

## autolam: Base-Material Solutions for Automotive Electronics

Automotive electronics technologies are evolving at an increasing rate. Paying attention to the properties of materials at the substrate level is the first step towards achieving the most stringent performance targets of today's automotive manufacturers. autolam offers the solutions demanded by the diverse and unique requirements of automotive applications today and in the future.

Mark Thompson

a number that you're going to want to have. Additionally, testing—not just electrical—but HIPOT, HAST, and all the other testing variables should be done. If you have a requirement for HAST testing, it's going to have to be on your drawing.

We also need to know the mask, ID color, and type. We have various dielectrics for our colors of masks. Why is that? We can't feasibly set up every possible color with the automatic flood coater. Some of them have to be hand-screened by an operator, and that person doesn't generate the pressure that the machine has. Ultimately, we may call blue or purple or red something closer to two mils of dielectric thickness over the top of the glass and one mil over the top of the metal. Does that make a huge difference on an eight and eight? Not really, but does it make a huge difference on sub-four and four? Absolutely. When you get down to the real small geometries, that additional mil of dielectric thickness and dielectric constant change for the solder mask makes a huge difference for controlled impedance.

Additionally, there are things like allowable X-outs and impedances. If you have any impedances, either call it out on a README or directly on your drawing notes. Typically,

it will say something like, "All five-mil lines on layers one, three, six, and eight to be 50 ohms." Now, one thing that I don't advise is chasing the impedances. We have a couple of our customers where if I send calculations, it will go back to the customer, and they will make those modifications down to the gnat's butt. They'll say, "If I say I need to change your 4-mil trace to a 4.25, I'm going to send data at 4.25." That doesn't mean that other fabricators would need that same change. If it's within 10%, don't mess with it at all. Remember that being the goal. As a designer, engineer, or layout person, they're just trying to stay within 10%. They give it to a fabricator, and we take it the next 10 miles.

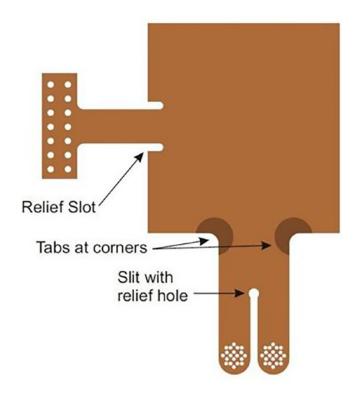

Then, there are cut-outs and radiuses. If you have a cut-out that is drawn or depicted as 90-degree intersections, we're going to need to know what the minimum radius is. Is it 0.032", 0.062", 0.093"? What's the minimum radius to be able to fit that device inside that cut-out? Those are just some of those kinds of things that I'm talking about. One thing that can eliminate the confusion between fabricators and people that are generating fab notes is consulting your fabricator. Call us directly and say, "I'm working on some fab notes, and my board is heat-sensitive. It is controlled impedance, and I need this. I have a 0.8-millimeter ball grid array, and I need to ingress and egress out of that very tight pitch BGA."

Now, at that stage, I have to ask, "Are you going to have long runs of very small lines and spaces for differential pairs that are ingressing and egressing out of that BGA? Or are you only necking down to a very small distance from a much larger differential size outside the BGA?" And the reason I say that is because I have a number of customers that will ask me. "What do I do to control the differential pairs that are inside that BGA?" If they're less than an inch and most components are an inch, two inches, in maximum size, it means nothing. I'd say, "Control those larger differential pairs that are running 12 inches on the outside of the BGA and not those that are inside the BGA." Take the hit of having it going inside that BGA.

**Shaughnessy:** Are the fab notes incorrect, or are they primarily just incomplete? What is typically the biggest problem?

**Thompson:** Gosh, we see everything. We have over 5,000 customers. We see inaccurate notes and notes that are not relevant to the job and therefore require a phone call. "It looks like you're calling out blind vias on this job, and there are no second drill files associated with a layer 1 to 2." If they don't exist, don't call them out. Simple as that.

**Shaughnessy:** It just amazes me because many of these designers have been doing this for 40 years. But a lot of times, fabricators just accept the data because you want the job, and you fix the problems.

**Thompson:** Even the new guard, the new kids that are coming into PCB design, just don't know what they don't know. I try to assist them in any way I can.

**Shaughnessy:** But it sounds like there are often no consequences to submitting bad fab notes.

**Thompson:** Other than the hit on time. Because either a salesperson or I have to call the customer and clarify those notes. That takes time, and we sell time.

Shaughnessy: You said you have your regular customers, and that you have them trained. What are some of the things that a trained customer will provide you?

**Thompson:** For example, nesting, which is how much prepreg is going to get sucked up based on the copper weight that is an interface on an inner layer. If it's half-ounce, it's going to have less of an impact. If it's two-ounce, three-ounce, or four-ounce copper, it's going to be a huge impact. It also depends on the configuration of the layer, whether it's a full signal, a split plane, or a plane. If it's a plane, it's going to have the least impact. If it's going to be a split plane, it's going to have more impact. If it's a signal, if it's a pure signal, two or three-ounce copper, and you're not calculating exactly how much break you're going to lose off that dielectric value, your impedances could be way off.

**Shaughnessy:** Happy, do you have anything to add?

Happy Holden: I spent my first 30 years not allowed to use IPC specs. Our many packaging specs were far more detailed than IPC, and they were written around our fabrication. Everything was being built in Asia—not in China, but in Asia, where the engineers were not native English speakers. I cleaned up a lot of their stuff with pictures and diagrams because using words constantly got us into trouble in terms of different translations. Each engineer might translate it differently.

**Thompson:** Exactly. And that brings up a really good point about the dielectric constant. I frequently get phone calls, where people will say, "What's the Dk of 370HR?" And I'll say, "What preg ply? What dielectric? What speed?" There are a number of different questions I'm going to have to ask to be able to get to where they want.

**Holden:** Because all these things are built out of different cores with different weaves of glass, which all have a different glass-to-resin ratio, and that's not even counting what frequency you're operating in.

**Thompson:** It makes a big difference between 500 megahertz and 120 GHz. With 120 GHz, that Dk goes way down.

**Holden:** I always start with material because that can get you in trouble. And if an RF amplifier is not working on a cellular tower in Louisiana in the middle of the summer, they blame the fabricator. Did you happen to understand that this material that you selected, when it's humid and hot, the loss tangent goes completely away, and your signals go away too? It has nothing to do with the board. It's the fact that you didn't understand enough about

the material you were selecting before you did it. Or you didn't bother to test the extremes in your simulation and things like that, which I've always faulted the EDA tools.

EDA tools let us put in a dielectric constant, and then those same EDA tools will come up with a thermal analyzer to ensure the difference in temperature on the board. And yet the impedance calculator and field software they have only allows one dielectric constant and no allow-ability to put in a slope between the temperatures that you just told me the boards are going to see anyway. That dielectric constant dissipation factor's not going to

be the same at those different temperatures, as well as frequencies. Yes, we understand temperature gradience, but somehow, nobody's ever accepted the fact that there is an electrical performance gradient.

They consider materials to be constants or absolutely flat lines; it's not going to change temperatures, and not going to change the frequency or anything else. And they do all of their signal integrity and impedance analysis based on this assumption about material. And with FR-4, that couldn't be further from the truth. You can get some really expensive material that's relatively flat, but it's really expensive. I keep asking EDA people that question, and they just shake their heads and say, "Nobody's asked for it."

**Thompson:** Happy brings up another good point there. We have two facilities: Redmond, Washington, and Tucson, Arizona. And you can imagine that Washington is moistureladen. It's rainy most of the time and very cool, which is vastly different from Tucson, where it is extremely hot and dry. The press parameters and temperatures are vastly different between our two facilities. Therefore, the effective dielectric constants of the materials we use

vary. And that's all over the map. Recently, I've been gearing over to helping with Tucson more. I use Tucson's effective dielectric constants on their materials and their dielectric press values, which are different than what we use here in Redmond.

Barry Matties: Pretty much every job that comes in has data that's inaccurate or missing.

**Thompson:** Absolutely. Even having gone through sending a customer effective dielectric constants and calculations and dielectric builds, it does not preclude the customer from

> changing things and submitting data that has vastly changed. They may say, "Five mil lines for 50 ohms." We get the data, and now they're eight mil lines. And the dielectrics are vastly different. Not only does that happen, but we also get people asking for different colors. Originally, it was calculated as green, but now it's going to be calculated as black—or worse vet, white.

In fact, all of the material colors—from green to blue, red, purple, and black—are all an approximation of 3.9 at 1 GHz. The white, for whatever reason, is 6.3. It's virtually double the dielectric constant. And why is that? Years ago, when people were doing more whiteboards for RF type considerations, they had problems where they were covering whatever the substrate was, or the surface finish was.

**Matties:** When you get the fab note, though, part of the conversation we've had with you and others is there's no incentive for them to send you a package that's 100% accurate or complete because the fabricators will do the work. And if you don't, the customer will just go and find another fabricator that will.

Thompson: But do you really want a fabricator to tweak your stuff? That's really the guestion you have to ask vourself. Do vou really want the fabricator to tweak with your stuff to the point where they're making a two- or threemil change of their signal to be able to accommodate the impedance?

**Matties:** You could say no, but apparently they

don't mind if what we're hearing is accurate. How do we get designers to do it right the first time?

**Thompson:** More training, I'd say.

**Matties:** Part of it is more training, but is the information available that they need to provide the fab notes that you need, or how do they go about getting that?

**Thompson:** Most of them use templates that are boiler notes that they have straight from their CAD system. Altium, for instance, has a template that has boiler notes that they can go in and they can massage, if you will, to fit the needs of their particular board.

**Matties:** Is it board-specific, or is it fabricatorspecific too?

**Thompson:** It's board-specific—not fabricatorspecific. Fabricators are vastly different. Even between our two facilities, I just made the point about temperature and humidity driving a big change between our facilities.

**Shaughnessy:** But designers must be aware of the difference in humidity in Seattle vs. Tucson, right? It seems like this goes back to our discussion about whether designers need to be experts at manufacturing. Nobody sets out to design a board that isn't manufacturable. These

people have been doing it for 35-40 years, but they're still going around in circles with data.

**Thompson:** When they do a whiteboard process and go through an engineering review, and they say to themselves, "We're going to have to drive this down to six-mil vias." Now, sending it to us with a six-mil via, if they want it epoxy-filled, we're going to have to

increase that between 0.008" and 0.20." That's the sweet spot for us for epoxy fill. How do we get there? All of what we've been talking about is only relative to signal integrity. What about the things that they are grossly neglecting, such as missing drill files, IPC netlists, and layers? We'll have a 10-layer board, and we'll just get outer layers. Where are the inner layers?

**Shaughnessy:** Right. But if they're using an EDA tool, doesn't the EDA tool sort of say, "You're forgetting this extra layer?" It seems like there would be something.

**Thompson:** You mean a DFM tool? Frequently, they get in such a hurry that they negate that process. It's sort of like saying, "We're going to send the space shuttle up, and we're going to forget about that particular process. We're not going to go through those 30 days of that particular thing for flight. We're just going to go ahead and push it and make it work," and that's when you end up having space shuttles blowing up.

Matties: Oftentimes, you invest six or seven hours, in some cases, just preparing to give them a quote, and you may not get the job.

**Thompson:** Sometimes, it's way more than that. At times, I'll have a series of 28 emails, and we won't get the job.

**Matties:** Do you consider that a marketing or cost-of-sales expense on your P&L? Is it attributed to your sales costs, or do you attribute it to engineering?

**Thompson:** It's attributed to engineering.

**Matties:** It seems to me that it should be attributed to cost-of-sales because that's all presale. You may be an engineer, but you're in the selling process when you're doing that. And if you're in the selling process, maybe you should get a sales commission.

**Thompson:** Our sales manager has always said that I'm one of his best salespeople, although I'm not an official salesperson.

**Holden:** It's too bad that most fabricators can't get away with charging non-referring engineering (NRE).

**Matties:** We've framed this conversation around fab notes, but there are also the fab notes for assemblers that we haven't even really talked about. This is just on the bare board side. And if it's this bad on bare boards, it has to be kind of rough for the assemblers too.

**Thompson:** Oh, gosh, yes. We have assemblers we'll send data check logs, and we'll have no less than five or six reCAMs based on small nuances that they want to make. They'll say, "Can you move the fiducials 0.5 mils in

this direction? Can vou make the rails this size? Can you change this to a score tab instead of a breakaway tab?" All these different things that should have been negotiated from the beginning and came in through sales as a complete package with an assembly drawing or a sub-

panel drawing. Some of them refuse to produce sub-panel drawings for that very reason; they reserve the right to be able to come back and say, "Our nebulizer bit needs at least two inches before I can start to pinch these tabs off."

Over the years, we've understood those requirements, and we put together what's called a CSR database—or customer special requirements database—that has all the hot buttons for all 5,000 customers of ours. If they say they need a specific shipping method, if they have a specific assembly method, they have a specific panelization method, it is understood. And all of the departments are required to look at their section in the CSR database and to be able to conform to that.

**Shaughnessy:** Is there a standard for fab notes? That's one of the things we heard from previous conversations is that there really is no standard. Designers create the fab drawings the way they want to do them.

**Thompson:** Ultimately, I gave one customer 10 different scenarios of how to panelize things nesting, 180-degree rotations, various breakaway tab strategies, the size of perforations and tabs along with the size and location of score lines. Because some people want the scoreline inboard, and some people want them outboard. Having them outboard means that they have nubs that they're going to have to trim off after assembly, and a lot of folks don't want to have to do that either. It becomes guite cumbersome. **Shaughnessy:** Do you all advertise your capabilities? Because that's one of the things we've heard: Some board shops don't want to put out their capabilities because they're afraid it's IP that's going to help their competitors.

**Thompson:** We absolutely do. We have a capabilities matrix, and we talk about all of the things that we would need to build a circuit board.

**Matties:** From what we hear, the fab notes are a problem, and there's no good solution. Is there a lack of incentive since you fix all their mistakes anyway?

**Thompson:** It really comes down to time and training working with a customer. I've worked with some customers for over 23 years, and some of those customers will send us precisely what we need every time. Some of them that are relatively new will send us the wrong data almost every time.

**Matties:** What is the benefit of sending data correct the first time?

**Thompson:** We sell time.

**Matties:** But there's more than just time, right? If you were to make a pitch to a designer on fab notes and why they should provide 100% accurate on-time to you, what would that sales pitch be?

**Thompson:** It could be a number of different things, such as time to market, for instance. If you work a new project and need time to market, you must ensure that those fab notes are accurate because if they're not, you're going to get boards that aren't going to perform for you.

**Shaughnessy:** What would you recommend to somebody who's a brand-new designer as far as creating fab notes?

**Thompson:** I've said this before, but consult your chosen fabricator and ask them to assist you in the generation of the fab notes. Now, having said that, only the customer ultimately knows

> what their performance characteristics need to be for that particular board. There are many hidden things that the customer may not tell us, such as heat considerations. Signal integrity is just one small part of it. And maintaining controlled impedance is easy. Fabricators can do that day-in, day-out. But where it becomes difficult is those things that they don't tell us that they need on their boards that they

will not divulge due to NDAs or other reasons.

**Matties:** It's a big topic with a lot of room for improvement.

**Thompson:** Exactly.

**Matties:** Thanks so much for your time, Mark. We appreciate it.

Thompson: Thank you. DESIGNOO7

To read past columns or contact Thompson, click here. Thompson is also the author of *The* Printed Circuit Designer's Guide to... Producing the Perfect Data Package. Visit I-007eBooks. com to download this book and other free, educational titles.

# Be Aware of Default Values in Circuit Simulators

### Quiet Power by Istvan Novak, SAMTEC

Simulators are very convenient for getting quick answers without lengthy, expensive, and time-consuming measurements. Simulators range from simple spreadsheet-based illustration tools [1] to very sophisticated 3D field solvers [2]. Somewhere in the middle, we have the generic circuit simulators—the most well-known among them being SPICE. Berkeley SPICE has been the grand-daddy of all SPICE tools [3], and these days, there are many professional SPICE variants available. These tools have been around for a long time, and we usually take the validity of their output for granted. While the tools may be bug-free, no tool can give us perfect answers for just any arbitrary numerical input; sometimes, we can be surprised if we forget about the numerical limits and the limitations imposed by internal default values.

As an example, I will show a few simulation results on a simple ladder-like power distribution network, all done with the free LTspice simulator [4] from Linear Technologies, now part of Analog Devices.

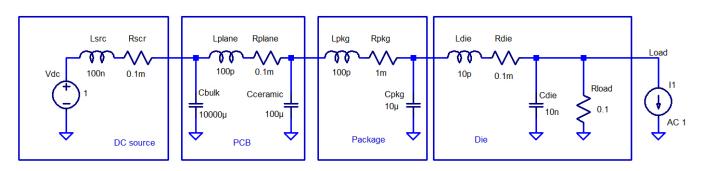

Figure 1 shows the schematic diagram of a simplified ladder model of a point-of-load power distribution network (PDN). The PDN is represented by four cascaded blocks. On the left is an ideal voltage source with series resistance and inductance modeling the DC source. To its right is a PI model of the PCB with plane resistance and inductance, as well as bulk and ceramic capacitors.

The next block describes the package with its series resistance, inductance, and capacitance. The 10- $\mu F$  capacitance value suggests that this is not only the static capacitance of the package planes, but it also represents package capacitors. The last block on the right describes the die with a series RL term, a parallel capacitance, and a parallel load resistance, which is determined by the nominal voltage and the average power consumption.

Outside of these blocks is a 1A AC current source injecting test current into the silicon node. Since all elements are linear and timeinvariant models, the actual current value does not matter, but the 1A value is convenient

.AC DEC 10MEG 10G 500 .SAVE V(Load)

Figure 1: LTspice schematics of a simple PDN.

### Pcbcart

# Get Your PCBs Assembled within Budget and Time Schedule

#### **Production resumed!**

PCBCart's Consigned & Turnkey Circuit Board Assembly services let you get fully assembled PCBs at lightning speed and low cost without compromising quality.

#### **Our Advantages:**

- Prototype, low-to-mid volume, production run

- SMT, THT, Mixed Assembly technologies

- Supported parts: BGA, QFN, 01005, 0201...

- Value-added options: Free DFM, AOI, AXI...

www.pcbcart.com sales@pcbcart.com

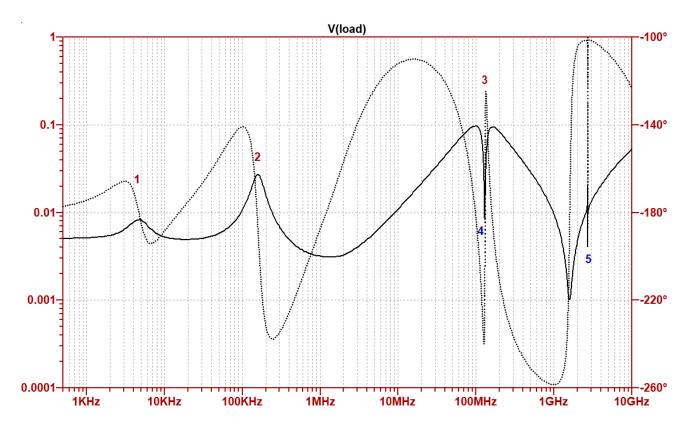

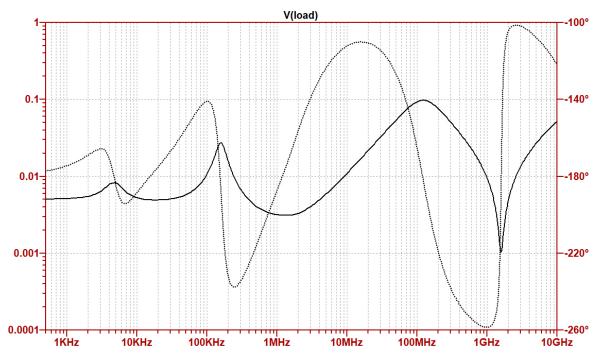

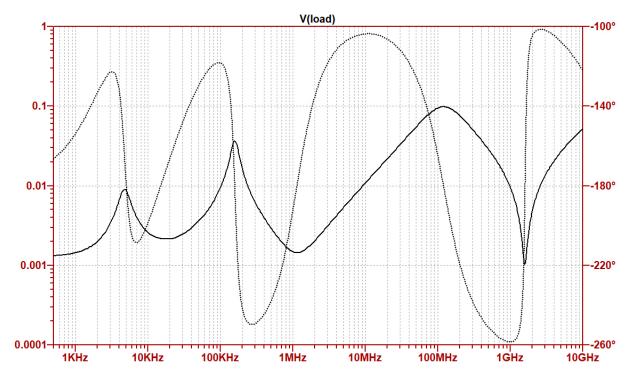

Figure 2: Impedance magnitude and phase of the simple PDN shown in Figure 1.

because the simulated V (load) output voltage directly gives us impedance without the need for further scaling.

Figure 2 shows the result. The heavier line is the impedance magnitude with its scale on the left, the phase is the thin line with its scale on the right. We see four resonance peaks and one sharp dip on the plot. Peaks 1, 2, and 3 come from the antiresonances of neighboring capacitor banks. For instance, the first peak is formed by Lsrc and Cbulk, and the LC parallel resonance of the 100-nH and 10000-μF values produce the 5-kHz resonance peak. To find the second peak, which comes from the series inductance of the Cbulk capacitor and the capacitance of Cceramic, we need to know the assumed inductance of Cbulk.

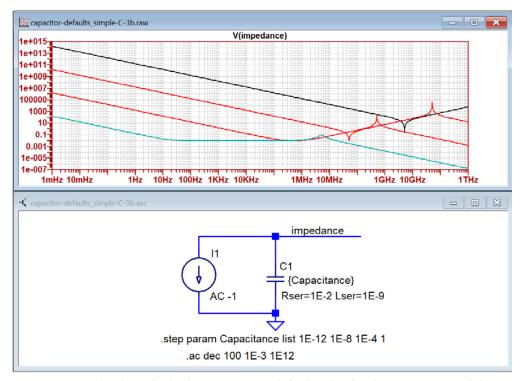

You can notice that there are no series resistance and inductance symbols in series to the capacitors, so does it mean the simulation assumes zero values for those parasitics? In this regard, LTspice is unique among the SPICE circuit simulators. We can specify the usual simple parasitics without adding the corresponding schematic elements.

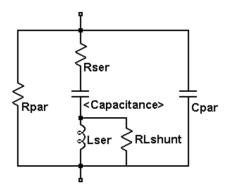

The equivalent circuit, as defined in LT Wiki [5], is shown in Figure 3. We can specify not only the equivalent series resistance and inductance but also two parallel loss elements and a body capacitance. These parameters will be frequency-independent entries. But how do we enter these parameters if we don't want to type up the SPICE deck manually?

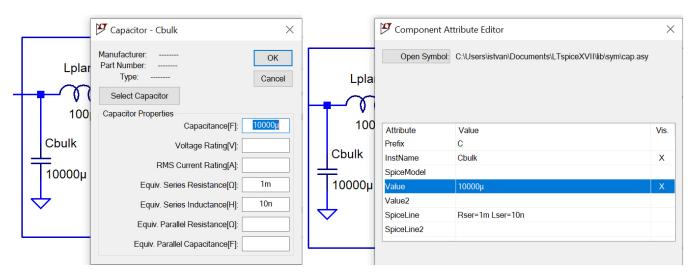

LTspice makes it easy, offering multiple options. Figure 4 on the left shows what happens if we move the cursor over a capacitor in the schematic diagram and right-click. A window pops up where we can manually enter various attributes. On the right, you see the window which pops up when you hold the control key while you right-click.

The two windows offer somewhat different choices. On the left—in addition to the equivalent series resistance, inductance, and body capacitance—we have only one parallel resistance entry. On the right, we can enter every parameter listed in Figure 3, including the initial condition, temperature, and the multiplier (m or x), which is a convenient way to simplify the schematics if we have m number of iden-

#### C. Capacitor

Symbol names: CAP, POLCAP

Syntax: Cnnn n1 n2 <capacitance> [ic=<value>]

+ [Rser=<value>] [Rpar=<value>]

- + [Cpar=<value>] [m=<value>]

- + [RLshunt=<value>] [temp=<value>]

It is possible to specify an equivalent series resistance, series inductance, parallel resistance and parallel shut capacitance. The equivalent circuit is given below:

Figure 3: Screenshot explaining the capacitor equivalent circuit in LTspice.

tical capacitors connected in parallel. We can also hide parameters or make them visible on the schematic using the checkmark in the last column.

For the schematics shown, I turned on the feature only for the capacitance value; otherwise, the view would become very crowded. Notice that in Figure 4, I show the actual parasitic values that were used to generate Figure 2.

|           | Cbulk  | Cceramic | Cpkg | Cdie |

|-----------|--------|----------|------|------|

| C [F]     | 10000u | 100y     | 10u  | 10n  |

| ESR [Ohm] | 1m     | 0.5m     | 10m  | 1m   |

| ESL [H]   | 10n    | 100p     | 1n   | 1p   |

Table 1: Parasitic values of capacitors that were used to generate Figure 2.

Now, we see that the series inductance of the bulk capacitor is 10 nH, and this creates the anti-resonance with the 100-µF ceramic capacitor. From these two values, we get a 150-kHz antiresonance frequency, and that is exactly where Peak 2 is. Peak 3 is at 150 MHz, and it appears to be split by the sharp and deep Notch 4. Table 1 summarizes the capacitor-parasitic values for all four capacitors.

We may wonder if the values in Table 1 represent reality because ESR and ESL for the ceramic capacitor appear to be unrealistically low. Yes, it would be unrealistic to expect these values from a single capacitor, but if we imagine that these values represent ten pieces of 10-µF ceramic capacitor with 5-mOhm ESR and 1-nH ESL in each, then it looks reasonable.

If we move on to look at the resonance at Peak 3, we realize that it is formed by the 10-nF Cdie capacitance and the equivalent inductance of the entire network looking back from the silicon, which is the well-known die-package

Figure 4: Options to enter parasitic values for capacitors in LTspice.

Figure 5: Impedance magnitude and phase of the simple PDN showed in Figure 1, but all parallel body capacitance is set to zero.

resonance. By the time we properly add up all series and parallel inductances, it comes out around 160 pH. The antiresonance with the 10-nF Cdie value comes out close to 100 MHz, where the split antiresonance peak happens.

We still need to understand where the two extra resonances—Notch 4 and Peak 5—come from. To get the answer, we need to go back to Figure 4 and check what happens with the parameters that we did not fill out. On the left, there are two parameters we left empty: parallel capacitance and parallel resistance. What happens if we explicitly set the body capacitance to zero? The result is shown in Figure 5. Notch 4 and Peak 5 disappeared, but the rest remained practically unchanged.

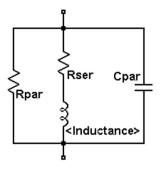

Now, the resonance pattern makes sense, but there is still something happening. Why do we have 5-mOhm impedance at low frequencies, when the circuit calls out only 1 mOhm and three times 0.1-mOhm resistor values in the series path, altogether 1.3-mOhm series resistance? We need to look at the definitions of the inductors. The definition of inductor attributes is shown in Figure 6 [5].

In the same way we did it for the capacitors, we can call up the parameter-entry windows for the inductors as well. In Figure 7, we see two parasitic components listed: series resistance and parallel capacitance. We also see a note at the bottom of the left window. There is a 1-mOhm default value for the series resistance. This means if we do not make an

#### L. Inductor

```

Symbol Names: IND, IND2

Syntax: Lxxx n+ n- <inductance> [ic=<value>]

+ [Rser=<value>] [Rpar=<value>]

+ [Cpar=<value>] [temp=<value>]

```

It is possible to specify an equivalent series resistance, series inductances, parallel resistance and parallel shut capacitance. The equivalent circuit is given below:

Figure 6: Equivalent circuit of inductor parasitics and attribute list.

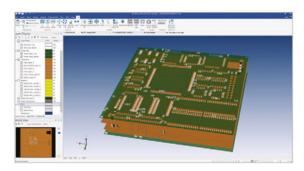

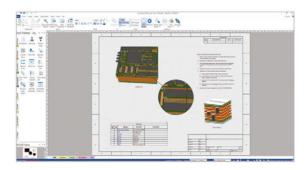

# Create Comprehensive PCB Documentation to Drive Fabrication, Assembly and Inspection

## BluePrint-PCB

BluePrint automates the PCB documentation process, creating comprehensive electronic drawings, successfully driving the procurement, fabrication and assembly process.

- 3D technology allows visualization of imported CAD data as a 3D PCB

- Lowers documentation cost and time

- Increases documentation detail & accuracy

- Shortens PCB design cycles

- Reduces documentation time by 60-80%

- Improves manufacturing & simplifies inspection

Download your free e-book

"The PCB Designer Circuit

Designer's Guide to Assessing

Your PCB Documentation

Process"

**CLICK HERE TO DOWNLOAD**

This book, written by Mark Gallant of DownStream Technologies, explains how an automated documentation solution like BluePrint-PCB® can eliminate post-processing errors and speed up time to market.

This book is a must-read for any PCB designers or design engineers who would like to adopt 21st-century PCB documentation processes.

For more information visit downstreamtech.com or call (508) 970-0670

Figure 7: Parasitic definitions of the Lsrc inductor.