AN CONNECTOO PUBLICATION

**Documenting Intent With IPC-2581**by Amit Bahl

by Amit Bahl

**Tolerant of Tolerance?** *by Martyn Gaudion*<a href="p.26">p.26</a>

# **DOCUMENTATION**

THE best way to find a PCB fabricator, anywhere.

## NATIONAL TECHNOLOGY, INC.

Rolling Meadows, Illinois, U.S.A.

Contact Me

Overview

Contact

Specs

About

Videos

**Photos**

**Brochures**

News

National Technology, Inc. is a multi-facility manufacturer of single sided, double sided and multilayer (up to 18 layers) Printed Circuit Boards, with locations in Rolling Meadows, IL and Gandhinagar, India. We have the capability to support quick turn prototypes (24 hour to 10 day) and standard production lead-times of 3 weeks.

Markets: Automotive, Communication, Computers,

Consumer, Industrial, Medical

**Board Types:** Single-sided, Double-sided, Multilayer

Mfg Volumes: Prototype, Small, Medium, Large

Other Services: Quick turn-around

Specialties: Blind/buried vias, Controlled impedance

Certifications: ISO 9001, ITAR registered, RO compliant, UL

Click to see a partial list of registered OEMs!

Click here to see a demo

# Why YOU should Showcase:

- Capabilities listing for advanced search functionality

- Specialties and certifications listing

- Ability to upload brochures and videos

- Quick and easy "Contact" and "RFQ" buttons

- News, web and contact links

www.thepcblist.com

CONFERENCE & EXHIBITION > March 25-27, 2014

MEETINGS & EDUCATION > March 23-27, 2014

MANDALAY DAY DECORT AND CONVENTION CENTED

MANDALAY BAY RESORT AND CONVENTION CENTER LAS VEGAS, NEVADA

WWW.IPCAPEXEXPO.org

# Design-Focused Education March 21–24, 2014

# NEW IDEAS...FOR NEW HORIZONS

- **DESIGN FORUM** Educational program featuring presentations by experts in design

- PROFESSIONAL DEVELOPMENT COURSES Three-hour classes led by subjectmatter experts

- DESIGNER CERTIFICATION PROGRAM Basic (CID) and advanced (CID+)

- EXHIBITION More than 400 exhibitors displaying technology equipment and products.

For more information on design-focused programs, visit www.IPCAPEXEXPO.org/DESIGN.

# This Issue: DOCUMENTATION

# **FEATURED CONTENT**

The layout is finished, but now it has to be documented for manufacture. What's the best approach to ensuring your fabricator builds the board exactly the way you intend? Find out in this issue of The PCB Design Magazine, when veteran contributors Mark Gallant, Martyn Gaudion, and Amit Bahl focus on what happens after layout.

# 12 Mitigating the High Cost of **PCB Documentation**

by Mark Gallant

# **26** Tolerant of Tolerance?

# **FEATURE COLUMN**

**20** Documenting Intent With IPC-2581

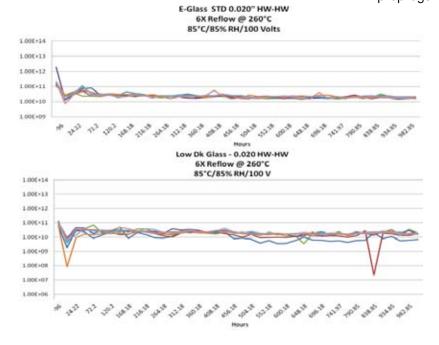

# Discover the Best-in-Class Laminate for High Voltage, Tight-pitch PCB Designs

# **I-Speed® High Speed Digital Materials**

I-Speed laminate and prepreg products are manufactured with Isola's patented high-performance multifunctional resin system, reinforced with electrical grade (E-glass) glass fabric. This system delivers a 15% improvement in Z-axis expansion and offers 25% more electrical bandwidth (lower loss) than competitive products in this space. These properties coupled with superior moisture resistance at reflow, result in a product that bridges the gap from both a thermal and electrical perspective.

# I-Speed CAF Test Vehicle Results

- Passed: 85°C/85% RH/100V after 1,000 hours at 0.65 and 0.75 mm pitch

- Passed: 35°C/85% RH/10V after 500 hours at 1.0 mm pitch

# **I-Speed Features**

- Global constructions available in all regions

- Optimized constructions to improve lead-free performance

- Improved Z-axis CTE 2.70%

- IPC 4101 Rev. C /21 /24 /121 /124 /129

- A low Df product with a low cost of ownership

- VLP-2 (2 micron Rz copper) standard offering

- Offer spread and square weave glass styles (1035, 1067, 1078, 1086, 3313) for laminates and prepregs

NUMBER 3

the pcb design magazine. com

THE OPTIMUM

MAGAZINE

DEDICATED TO

**PCB DESIGN**

AN OI CONNECTOO PUBLICATION

# CONTENTS

### **VIDEO INTERVIEWS**

19 What's Stopping the Signals?

#### **ARTICLE**

**42 Properly Designing PCB Footprints**by Nicholaus Smith

# 30 Mark and Kelly on Value-Added Vendor Visits

# **COLUMNS**

8 Back to Vegas by Andy Shaughnessy

# **56** Steinberger Papers A Big Hit

- **50** Matched Length ≠ Matched Delay by Barry Olney

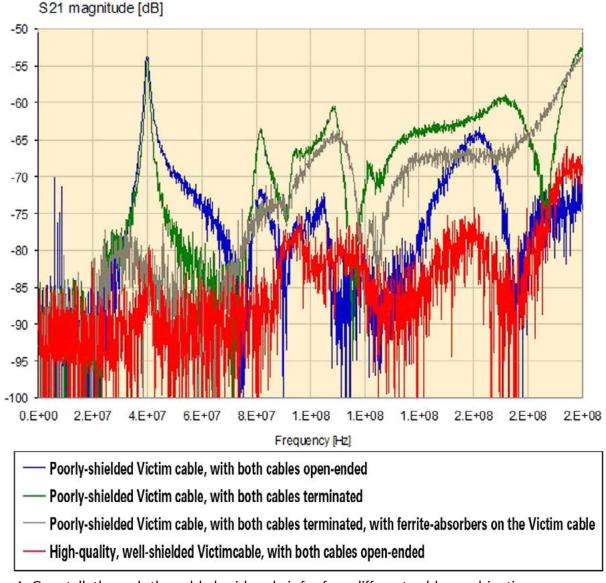

- 60 Checking Cable Performance with VNA by Istvan Novak

#### **SHORTS**

- **10 MIT Develops Herding Robots**

- 41 Optical Circuits Flexing Their Way to the Forefront

- 65 The Rise of the Monolithic 3D Chip

#### **NEWS HIGHLIGHTS**

- 24 PCB007

- 58 Mil/Aero007

- 66 PCBDesign007

### **EXTRAS**

**68** Events Calendar

69 Advertiser Index & Masthead

# Quality PCBs from the established industry leader

With over 40 years of experience delivering high quality PCB prototypes, Sunstone Circuits® is committed to improving the prototyping process for the design engineer from quote to delivery.

We lead the industry with an on-time delivery rate of over 99%. Plus, our on-site technical support is available every day of the year (24/7/365), giving Sunstone unparalleled customer service.

Get a quote instantly at Sunstone.com

- Live customer support 24/7/365

- Over 99% on-time delivery

- Best overall quality & value in industry

- In business for over 40 years

- Online quote & order

- Free 25-point design review

- RF / exotic materials

- Flex / Rigid-Flex boards

- RoHS compliant finishes

- Free shipping & no NREs

- PCB123<sup>®</sup> design software

- Controlled impedance testing

#### THE SHAUGHNESSY REPORT

# **Back to Vegas**

by Andy Shaughnessy

I-CONNECT007

Yes, we're heading back to Las Vegas for IPC APEX EXPO 2014. I, for one, will be glad to get back to Sin City.

I admit I was a little burned out on Vegas the last time APEX and the Designers Forum were held there, back in 2011. (That was BD, or before divorce.) We had been there for four years in a row covering the show, so I cheered when IPC announced that the event would be moving to San Diego for 2012 and 2013, and alternating every two years after that.

Now, don't get me wrong: San Diego is a great location. It's hard not to like a place that's always at the top of the annual "Top Cities in the Country" lists. And we did some sailing, which the desert pretty much precludes.

But after three years, it'll be nice to get back to Vegas. It's a microcosm of America, a symbol of all that is positive and negative in the land of red, white, and blue. This town is a true dichotomy: gamblers can win big, or lose big. There are a lot of really happy people on the way up, and a lot of not-so-happy people on way down.

Plenty of shiny casinos, and too many foreclosed houses.

Of course, Vegas presents its own unique challenges. My co-workers and I spend most of the week bathed in artificial light. We get up early, and by the time we finish work, it's night-time. Years ago, Editor Marcy LaRont dubbed us "The Mole People," because we went for days at a time without ever seeing the sun. I was afraid we might develop the bad eyesight that moles are famous for.

And you'd better wear your walking shoes for trade shows in Vegas. Mandalay Bay is a great venue, but it's so big that you just about need a GPS. Everything you need is a quarter mile away from your current location. One Mandalay Bay staffer told me that the show floor is almost half a mile from the front door.

Still, I'm glad to be heading back to Vegas. This year, APEX kicks off with the Designers Forum on Monday, March 24. Speakers include Greg Munie of IPC, Karen McConnell of Northrop Grumman, Gary Carter of Fujitsu

# More and More PADS Users are Switching to Altium Designer

Get the Benefits of Switching Today

#### **BACK TO VEGAS** continues

Network Communications, Dieter Bergman of IPC, Mark Laing of Mentor Graphics, Humair Mandavia of Zuken, and Ben Jordan of Altium.

Guest Editor Kelly Dack and I will be shooting video interviews for our Real Time with... Designers Forum program, and we'd love to interview you on camera. I've noticed that more and more PCB designers and design engineers are video-savvy; many of you handle yourselves well in front of the camera, and you don't freak out when the red light comes on.

It's really not much different from speaking to the other members of your department. But even if you're reluctant about being interviewed on camera, we can work with you. And if you're a PCB designer, I guarantee that you have a story worth telling. It does get easier over time. My first interview was a disaster, but we gave Charlie Capers and the rest of the staff at Trilogy Circuits something to chuckle about!

# The Survey Says...

This month, don't miss "The Town Crier." The inaugural column by our newest columnist, Dan Smith. Dan is a principal technologist at Raytheon, and a 33-year veteran of software design firms and military contractors. He has worn a lot of hats: PCB designer, programmer, product architect, and professional piano player.

Dan, "The New Mr. HDI," was handed the HDI torch by Happy Holden, and he leads the PCB HDI—Next Generation group on Linkedln. He has a passion for PCB design, especially design education. He's taught the PCB design process internationally, and he's led IPC's HDI certification efforts.

In this month's column, Dan delves into the state of PCB design instruction, and he wants your feedback. Take a few minutes to complete Dan's short survey on PCB design and design education. I know you're busy, but this won't take long. Then, Dan will discuss the survey results in his column over the next few months. This issue is too important to cover with just one column.

Dan welcomes your e-mails, but don't be surprised if your name shows up in an upcoming edition of "The Town Crier."

See you in Vegas! PCBDESIGN

Andy Shaughnessy is managing editor of The PCB Design Magazine. He has been covering PCB design for 13 years. He can be reached by clicking here.

# **MIT Develops Herding Robots**

Writing a program to control a single autonomous robot navigating an uncertain environment with an erratic communication link is hard enough; write one for multiple robots that may or may not have to work in tandem, depending on the task, is even harder.

This May, at the International Conference on Autonomous Agents and Multiagent Systems, researchers from MIT's Computer Science and Artificial Intelligence Laboratory (CSAIL) will present a new system that stitches existing control programs together to allow multiagent systems to collaborate in much more complex ways.

Researchers are currently testing their system in a simulation of a warehousing application, where teams of robots would be required to retrieve arbitrary objects from indeterminate locations, collaborating as needed to transport heavy loads.

"In [multiagent] systems, in general, in the real world, it's very hard for them to communicate effectively," says Christopher Amato, a postdoc in CSAIL and first author on the new paper.

"What typically happens is, the programmer

decides that red light means go to this room and help somebody, green light means go to that room and help somebody," Amato says. "In our case, we can just say that there are three lights, and the algorithm spits out whether or not to use them and what each color means."

# We Deliver...A 5-Star Performance

At U.S. Circuit, we are UL Certified to build hybrid construction with Rogers/FR408 family & Rogers/370HR as well as Isola I-Speed materials.

Manufacturer of Printed Circuit Boards

U. S. Circuit, Incorporated 2071 Wineridge Place Escondido, CA 92029 Ph: (760) 489-1413 Fax: (760) 489-2965

www.uscircuit.com

# **Superior Quality Superior Service**

ITAR Registered

ISO 9001:2008

# Mitigating the High Cost of PCB Documentation

by Mark Gallant DOWNSTREAM TECHNOLOGIES

The goal of minimizing the time and cost for engineering a new product and getting it to market before the competition is a constant struggle for developers of leading-edge electronic products. The complexities of the electronic component supply chain, reductions in qualified staff, and managing globally distributed engineering teams are just a few of the challenges. Eliminating bottlenecks can dramatically reduce concept-to-production time in a product life cycle. This is the Holy Grail in the quest for corporate efficiency.

To reduce or eliminate these bottlenecks in new product development, many electronic engineering teams are looking inward and reassessing the efficiency of their product engineering process. From concept to design, fabrication, and assembly, there are process inefficiencies that result in delays. The usual excuse for not reassessing, "This is the way we have always done it," may be a sign of complacency in an inefficient engineering process.

Quite often the assessment involves an evaluation of the current EDA tool set proficiency. Frequently, these tool evaluations evolve into an assessment of how their current tools perform against competitive tools. Loyalty to the incumbent EDA provider is a lesser consideration than the efficiency of the tool. As a result, entrenched EDA suppliers are forced to perform benchmarks for current users or risk a decline in their customer base.

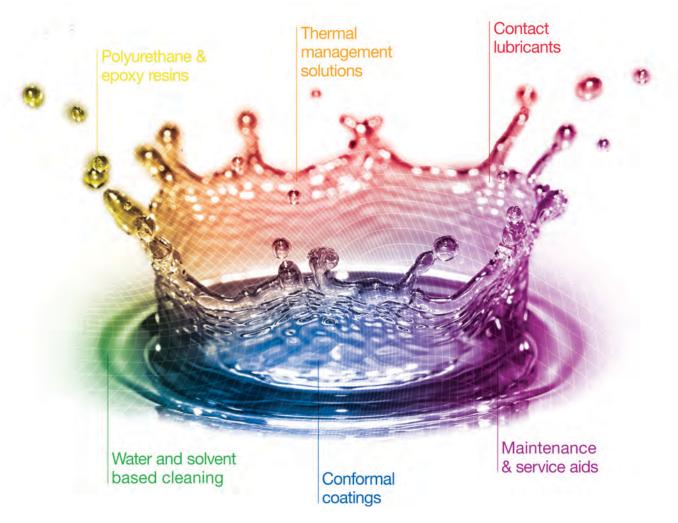

# In electro-chemical solutions, we reign

In the formulation, manufacture and supply of conformal coatings, thermal pastes, encapsulants, cleaners and lubricants, we have the solution. Through collaboration and research, we're developing new, environmentally friendly products for many of the world's best known industrial and domestic manufacturers – always to ISO standards.

Combine this unique ability to offer the complete solution with our global presence and you have a more reliable supply chain and a security of scale that ensures you receive an exemplary service.

Isn't it time you discovered how Electrolube can serve you? Simply call, or visit our website.

Tel: 888-501-9203 www.electrolube.com

### The Evolution of EDA Tools

In the CAD revolution of the 1980s, software-based EDA tools facilitated the migration from light tables and drafting boards to rooms full of hardware and software from best in class EDA tool providers. When one component of the EDA tool set was deemed inefficient, it was replaced with a more efficient tool from a litany of niche EDA tool providers. However, there was an inherent inefficiency in the interoperability of tools from different EDA tool providers. Integration was rudimentary at best, and often managed by the end-user. Poor tool integration was a key factor during the EDA provider consolidation in the 1990s as mergers and acquisitions forever changed the

EDA landscape. The number of tool providers shrank dramatically, and the multi-provider EDA tool set slowly morphed into a sole-vendor EDA tool set.

With the rapid adoption of a sole-vendor EDA tool methodology, new challenges arose. Being the largest EDA tool provider did not necessarily equate to being the best provider. Technological advancements and engineering process improvement goals often required tools not available from the core EDA vendor. In some cases, vendor offerings were just not suitable for the users' needs. Replacing inefficient or unsuitable components of a single-vendor EDA tool set imposed a significant challenge. Any new component must integrate seamlessly

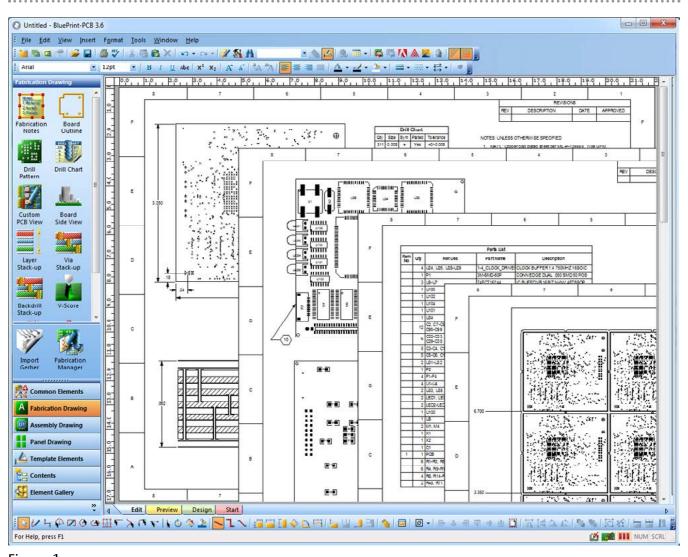

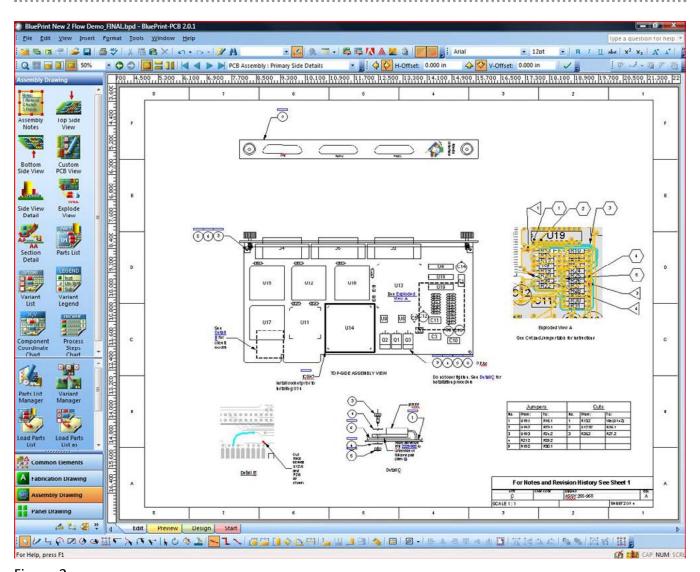

Figure 1.

into the current process and not disrupt the engineering process.

To facilitate this plug and play, engineering teams relied on user-developed custom applications. These applications served as the glue or patch cords between core EDA tools and niche third-party tools to create a manageable work flow. The pain of this methodology became obvious whenever an EDA tool provider required users to migrate away from their tried and true legacy tools to newer, more efficient tools. Typically, userware applications are written in a version specific scripting language. Legacy userware was incompatible and required herculean effort by specialized development resources

from a small talent pool to achieve compatibility with the new tool.

These resources were vital to maintaining a smooth engineering process, but they are not without their impact on new product introduction costs. The cost of implementing and maintaining integration of disparate tools was the impetus for industry standard file format specifications for data transfer, such as IPC-2581 and ODB++. Having a neutral file format endorsed and supported by all members of the EDA ecosystem facilitated data transfer among disparate tools.

EDA tools like schematic capture, digital and analog simulation, PCB design and layout,

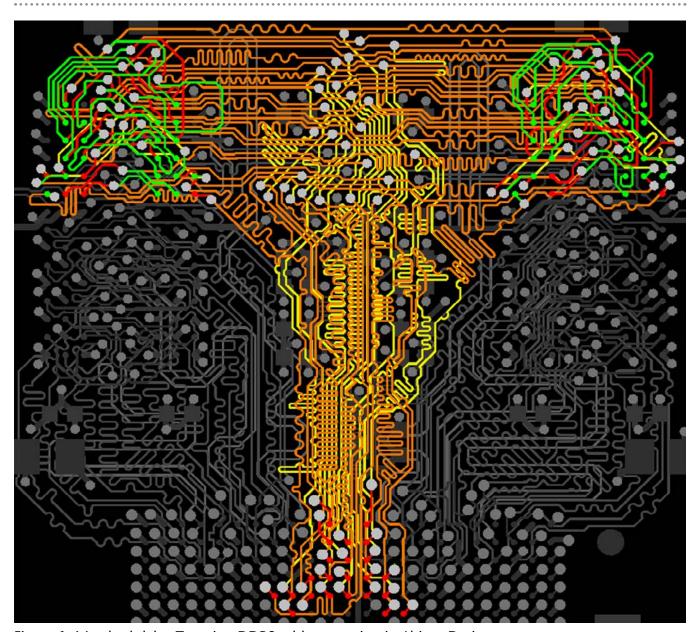

Figure 2.

autorouters, and others have matured, dramatically reducing time to market. But, even though most EDA tool providers have enhanced their tools through integration of new functionality or acquisition, some areas of inherent inefficiency in PCB CAD tools remain.

# **Post-Design Documentation:** Late to the Party?

One glaring example of this: The documentation required for fabrication and assembly of the PCB. Comprehensive PCB documentation is a requirement today, and if the end-product is destined for a military or aerospace user, the documentation requirements ratchet up considerably.

Yet the majority of PCB documentation is created using PCB CAD drafting features that have not improved since the CAD revolution of the 1980s. CAD tools are superlative at reducing the PCB design cycle, but they fall short on some of the most basic documentation tasks. For example, PCB design tools that sell for tens of thousands of dollars per seat lack the spell-checking found in \$99 word processor software. Most CAD tools lack support for a paragraph requiring the user to create multiline text strings as basic fabrication notes. Countless hours are spent using rudimentary drafting tools to create PCB detail views and drill charts, one segment or one line at a time.

These antiquated methods show their real colors during a design re-spin. Drill quantities out of sync in a manually drawn drill chart? Select the text string and edit the value. PCB detail view need updating because a component moved on the PCB? Either recapture the entire view or start editing the graphics one vertex or one segment at a time. Some engineering organizations have resolved to use popular MCAD tools to complete the PCB documentation. MCAD tools are superior to PCB CAD tools with respect to creating documentation.

However, converting the design to MCAD file formats results in disassembling the intelligent PCB CAD data. Parts are converted to shapes, traces to lines, copper shapes to polygons, and so on. Creating tables, notes, complex dimensions is certainly quicker, but culti-

> vating intelligent data for a parts list is no longer possible with

MCAD tools. Should a design re-spin be required, the MCAD drawings must often be recreated or manually updated with new design content. It also introduces an MCAD design database to an already crowded PCB documentation file collection. Maintaining synchronicity between PCB and MCAD design databases becomes the responsibility of

the user. The bottom line: Creat-

ing PCB documentation is not free or well automated in PCB CAD tools. Every PCB design has its share of tasks related to documentation. Some documentation sets can be dozens of drawing sheets. Stringent documentation standards for military, aerospace, automotive and other segments require highly detailed, timeconsuming documentation sets. Documentation requirements are not limited to one department across an entire organization. Many downstream

processes in product manufacturing have unique documentation requirements. This includes PCB rework instructions, assembly process steps, PCB panel fabrication drawing, assembly inspection, and more. There is more to a PCB documentation set than a simple one-sheet assembly and fabrication drawing. All of these

With our online system, getting quotes and placing orders is fast, simple and convenient. In fact every step of the process can be managed online–even payment! And our quality is guaranteed.

All you need to get started is to set up your account.

Create free account

documentation requirements should be part of any documentation efficiency calculation.

When considering the efficiency of your PCB documentation process, you must measure both creation and maintenance of a complete documentation set for the full life cycle of the product. A new product's documentation cycle typically begins at the prototype stage. From there, the number of documentation iterations can easily reach double digits. Consider that each iteration of a documentation set has both tangible and intangible costs, the greatest tangible cost likely being the salary of the individual creating the documents. Assuming an average PCB designer salary of \$75,000, and 20% of his time devoted to originating documentation, annual documentation costs will average \$15,000 per designer. That amount does not include time spent revising original documentation or documenting rework instructions to update in-house product inventory.

If we assume that revising a document takes 50% of the time it took to originate, add another 10% or \$7,500, and your annual documentation costs rise to \$22,500, a hefty sum if you are creating a basic two-sheet documentation set. Developing military standard PCB documentation can usurp more than 40% of a PCB designer's time. For those products, the cost of creating and

maintaining documentation can easily escalate. Some engineering organizations operate without dedicated PCB designers and require electrical engineers to complete the PCB design process. Because the average salary of an electrical engineer is higher than that of a PCB designer, this could factor into the high cost of creating documentation.

There are also intangible costs that are difficult to quantify. An inefficient documentation process that results in delays or a lengthy

new product introduction process

bears lost opportunity costs. Errors in the documentation set can result in multiple unplanned documentation revisions, re-spins of the PCBs, and errors in the assembly or part procurement process. Having a PCB designer focus 20% or more of his time on documentation rather than PCB design will delay the start of the next PCB design project. Sharing a networked PCB design product license to create documentation and design PCBs may require users to postpone critical tasks until product licenses are made available.

To mitigate the cost of documentation, begin by evaluating your PCB documentation tools and considering how well meet your documentation requirements. Using a PCB CAD tool with minimal support for basic documentation tasks may require additional effort for working around its shortcomings. For example, what does it take to draw a complex layer stackup detail or multirow drill chart? How easily can these details be updated when the layer count is increased, drill counts are changed

or new drill sizes added? Secondly, you should examine the documentation process and documentation requirements across all members of your organization. Follow the documentation trail to learn how each member of the entire enterprise uses the documentation set.

**Developing military** standard PCB documentation can usurp more than 40% of a PCB designer's time. For those products, the cost of creating and maintaining documentation can easily escalate. Some engineering organizations operate without dedicated PCB designers and require electrical engineers to complete the PCB design process. Because the average salary of an electrical engineer is higher than that of a PCB designer, this could factor into the high cost of creating documentation.

Are they creating documentation to augment their process that is currently not part of your standard documentation set?

Over the course of the CAD tool evolution, the suite of tools required for PCB design has somewhat stabilized. Schematic capture tools are used for drawing schematics, simulation tools for analog and digital simulation, PCB design tools for circuit design, and so on. All are automated tools designed and maximized for a specific part of the electronic product design process. Automated PCB documentation tools are not new, but their use is not widespread. Many are still reliant on the outdated method of creating PCB documentation within the PCB CAD tool to meet their requirements.

You can't design a PCB with a schematic capture tool, so why are so many designers using a PCB CAD tool to create documentation? This is akin to manually routing each trace of a 16-layer 8,000 net PCB design rather than using automated routing. The results will be similar, but the effort far greater.

The old adage "Use the right tool for the job" rings true for PCB design and documentation. If you are creating PCB documentation today, you should consider dedicated PCB documentation tools, such as Mentor Graphics' Fablink or DownStream Technologies' BluePrint-PCB.

The benefits of using a dedicated, automated tool specifically designed for PCB documentation are many. As automation has reduced the tedious task of routing traces individually, so too have documentation tools reduced the tedium of creating and maintaining PCB documentation. An automated documentation tool can reduce documentation tasks, reduce errors, and offer greater efficiency. **PCBDESIGN**

Mark Gallant is senior product marketing manager at Down-Stream Technologies.

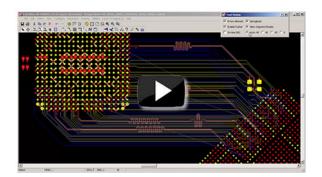

# video interview

# What's Stopping the Signals?

by Real Time with... PCBDesign007

What exactly is getting in the way of our signals, and what can we do about it? Lee Ritchey and Guest Editor Glenn Oliver explore the technological roadblocks that are blocking our signals.

realtimewith.com

### **DESIGN FOR MANUFACTURE**

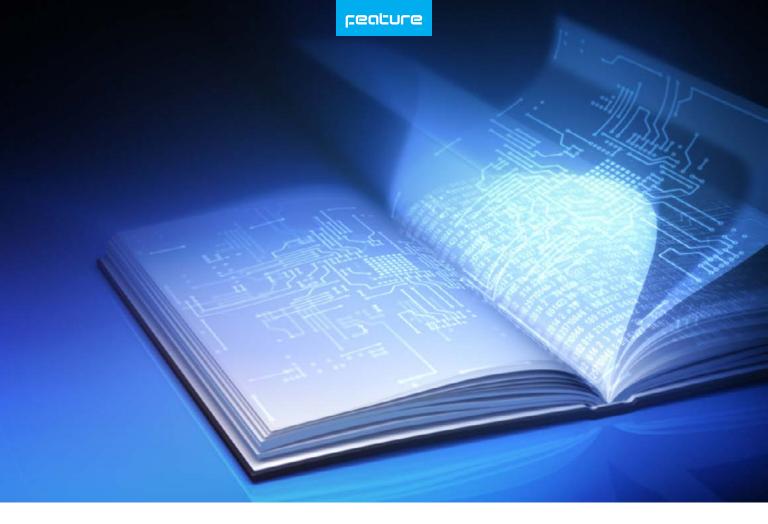

# **Documenting Intent With IPC-2581**

by Amit Bahl SIERRA CIRCUITS

Would a book be convenient if the chapters weren't bound, were scattered among different locations, required translation, and handwritten? That's akin to what PCB manufacturers face every day when piecing together Gerber files, drill files, board drawings, notations, netlists, BOMs, and pick-and-place coordinate files, to interpret what designers expect them to build.

That collection of files, none of which (except the Gerbers) share the same format, is almost always the way PCB designs are submitted for fabrication and assembly, except for a relatively few designs that are output in the ODB++

unified format. But salvation from the hodgepodge of design documentation is at hand, however, thanks to Revision B of the IPC-2581 standard for formatting PCB CAD data, which was released in late 2013.

In my November 2013 column, I wrote about how this standard consolidates all the data

single file that manufacturers can easily read, check to verify that the design is ready to build, and then use to drive CAM tools. The implementation of RevB by the CAD tool companies, DFM software vendors, and the CAM sector is underway. But there is far more in store for IPC-2581 to document designs as the standard evolves, as I learned from a recent conversation with Gary Carter. He is the senior manager of CAD engineering at Fujitsu Network Communications, and a founding member of the IPC-2581 Consortium.

> Carter first pointed to what the revised standard already enables. "With the PCB stackup section that's been incorporated in RevB, we've eliminated the need for a profile drawing entirely," Carter began. I won't steal his thunder about that provision, other than to say it will facilitate interplay between a PCB designer and manufacturing resources at the outset of a proj-

The upshot is that

the revised standard

now in place reduces

provides much more

build intent than the

legacy method of

conveying a design

to manufacture.

#### **DOCUMENTING INTENT WITH IPC-2581** continues

optimum stackup. He'll reveal the details on March 24 in a presentation at IPC APEX EXPO in Las Vegas. In fact, RevB eliminates the need for any drawings among the design data to convey build intent.

Carter explains, "We can render directly from an IPC-2581 file what otherwise takes several sets of drawings." He then re-

ferred to a network line card that has cutouts for optical modules, which was fabricated three-up per palette by several manufacturers as a demonstration project.

"There were the V-scores the number of files for and the mills and drills, export to just one, but which along with the stackup structure used to involve a couple of different drawthorough and coherent ing sets," Carter continued. documentation to clarify "Now, no drawings are required at all. You've got the specific tools spelled out in the file that are required for the V-cut, where those V-cuts are located, all described in a spec tied to that V-groove. The details on the milling outline can be described by '2581 so you know how that cutout is achieved.

And by the way, back-drill information is also conveyed by '2581, so there's no requirement to specify that in a separate file set."

The upshot is that the revised standard now in place reduces the number of files for export to just one, but provides much more thorough and coherent documentation to clarify build intent than the legacy method of conveying a design to manufacture. This will include assembly operations. But wait, there's more on the horizon.

Carter envisions a bridge to product lifecycle management (PLM) environments, which integrate all data about a product from a systems perspective from cradle to grave, including but far from limited to parts and production processes. As he explained, PLM is intended to be a part-centered view of any object, which encompasses all the attributes that define each part of the object and whether those part descriptions apply to the preliminary stages of product development, whether a part is actively being sourced for the product, or whether it is obsolete.

But Carter described a hook within the standard that could tie to more than hardware descriptions. "Contained in IPC-2581 is the abil-

ity to include external references to firmware configuration," he said,

> "so this is another aspect of the PLM story. I could export design data from my CAD tool into the PLM environment and thereby bring up a product configuration function that will be identified through the attributes I've assigned parts: 'Hey, I'm programmable. I need my reference guide to be related to a binary file that contains the program information that manufacturing needs to inject during the assembly process."

Most likely, the IPC-2581 file will merely point to an external file that could have a part number, which would be the program file.

Carter added, "I believe there's even the ability to inject that into a dictionary inside IPC-2581, but I don't think I would ever do that. It would add too much burden to the size of the design file."

He speculated about sometime merging such mechanical elements as 3D rotatable parts views with the IPC-2581 domain. That's a story for future iterations of the standard. Meanwhile, at the moment, RevB is the most flexible, comprehensive way to document a design so that a PCB manufacturer will understand exactly what you intend to be built. PCBDESIGN

Amit Bahl directs sales and marketing at Sierra Circuits, a PCB manufacturer in Sunnyvale, CA. He can be reached by clicking here.

BEYOND A SHADOW OF A DOUBT.

Dymax Conformal Coatings cure in seconds with UV light – and with ambient moisture curing available for shadowed areas, you can be confident you're getting maximum protection – even underneath components. Add vivid blue fluorescing for easy inspection of coating coverage, and you'll see more throughput, in less time, using less floor space. All with unsurpassed protection against moisture, dust, chemicals, and temperature cycling. And, they're backed by the Dymax Edge... an integrated offering of oligomers, customized adhesives and coatings, cure and dispense equipment, and application expertise that enables Dymax to deliver the best solution to the customer. Visit dymax.com/conformalcoating to download the new Guide to Light-Cure Conformal Coatings.

# **PCB007 News Highlights**

# **American Standard Circuits Earns** "Manufacturer of the Year"

U.S.-based circuit board manufacturer American Standard Circuits (ASC) has been awarded "2013 Manufacturer of the Year" by the Alliance for Illinois Manufacturing. The award is intended to showcase a company that serves as a testimonial to the Alliance's integrated business delivery model.

# **Viasystems Reports 10.9% On-year Sales Growth**

"We finished the year with some positive momentum that sets us up to continue to make progress on our cost structure in 2014, but in many ways I am glad that 2013 is behind us," said David M. Sindelar, CEO. "During the past year, we have worked through a number of challenges, including factory relocations, recovery from a fire in one of our largest factories, and new project launches, not to mention the economic pressures from reduced government spending."

# **Invotec Wins Formal ESA Approval**

The company is delighted to announce it has been formally awarded ESA approva—the first PCB supplier to achieve such approval in many years. Invotec already has a rich space heritage, manufacturing HDI and HDI flex-rigid boards for a variety of ESA and non-ESA space programmes to OEM specifications which, in many cases, go beyond current ESA approvals.

# **IPC: North American PCB Sales Continue Slow Recovery**

"North American PCB sales in December continued their slow recovery, while orders have been volatile," said Sharon Starr, IPC's director of market research. "In the current cycle, the book-to-bill ratio appears to have hit its low point in November and is now beginning to climb again."

# **Chinese PCB Firm DPMC Refutes Bankruptcy Rumors**

China-based printed circuit board manufacturer Dalian Pacific Multilayer PCB Co. Ltd (DPMC) has denied rumors that the company is going bankrupt.

# **IPC APEX EXPO 2014 Proves Leadership**; Space Sold Out

To visitors, the sold-out status means that the show floor will be busy and informative, with more than 425 exhibitors introducing new product technologies, innovations and demonstrations of the industry's newest advancements, many of which will also be highlighted in the dedicated New Product Corridor on the show floor.

# **MFLEX Doubles Sales to New Customers**

Reza Meshgin, CEO, commented, "Net sales to our newer customers more than doubled sequentially, and are expected to represent approximately 23% of total net sales. Looking ahead to the fiscal second quarter, we expect a significant sequential decline in net sales that we anticipate could approach 40%."

# **Dragon Circuits Intros Pure Gold LPC** for Medical Circuits

Texas-based circuit board manufacturer, Dragon Circuits (DCI) has announced immediate availability of their Pure Gold LCP, 100% pure gold traces plated on liquid crystal polymer (LCP) without the use of copper-base metals.

### TTM Reports Strong Q4 and FY 2013 Results

"We delivered strong results for the fourth quarter as seasonal revenue growth combined with solid execution resulted in increases in gross margins and operating profit," said Tom Edman, CEO. "Strong demand for our advanced HDI and rigid-flex PCBs drove our product mix shift toward advanced technology PCBs and brought our Asia Pacific factory utilization rates above 90%."

# **Global Flexible PCB Market to Reach** \$12.686B in 2015

The FPCB market was valued at \$11.321 billion in 2013, up by 9.4% year-on-year. In 2013, the most significant change in the industry was in the slumping profit margins of veterans and the soaring profit margins of new entrants. Market veterans lagged behind new entrants in equipment and technical R&D strength, according to market analyst Research in China.

# Leading the way for over 35 years.

# MARKET LEADING PRODUCTS

We are the United State's leading Printed Circuit Board (PCB) and Original Equipment Manufacturer (OEM). Our Products and services include:

Rigid PCB

Flex & Rigid-Flex PCB

LCP Pure Gold process

Design

Full-turnkey assembly

**View Our Products**

# INDUSTRY LEADING QUALITY

Our commitment to outstanding quality to each market we serve goes back over 35 years.

Our certifications include:

ISO9001:2008 AS9100C MIL-PRF-55110 & JCP ITAR IPC & UL

**View all Certifications**

Legendary manufacturing, service and engineering.

www.dragoncircuits.com | info@dragoncircuits.com | 972.790.7610

by Martyn Gaudion **POLAR INSTRUMENTS**

Wouldn't life be great if everything fit together perfectly? There would be no need for tolerance. However, for that to be the case, everything would need to be ideal and without variation. Therefore, unfortunately (or, maybe, fortunately), we all deal with measurements and materials and situations that are not ideal and are compromised in one way or another.

Often the challenge with tolerance comes down to misunderstanding, and the fact that we all now design with CAD tools which have levels of precision far in excess of the realisable parameters of the mechanical or electrical materials and measurement systems we deal with

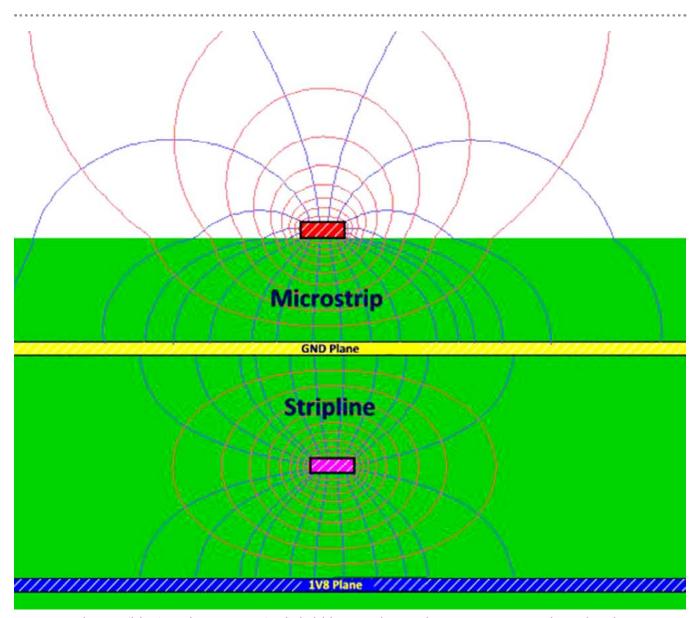

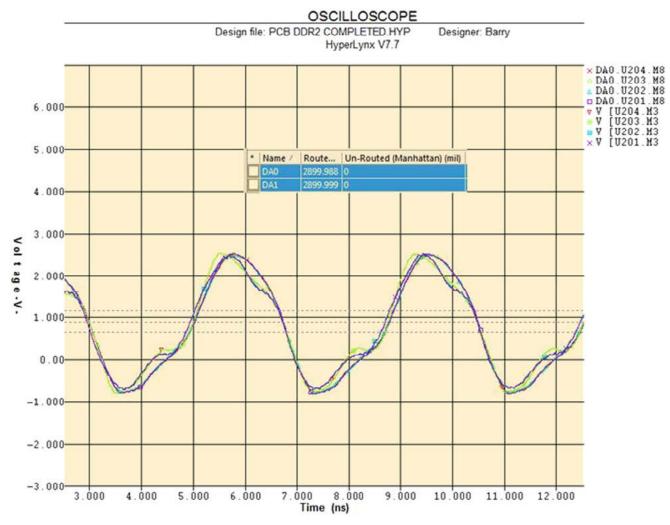

on a day-to-day basis. Poor understanding of tolerance or being intolerant of tolerance can lead to disappointment (see Figure 1).

Or, as attributed to Aristotle, "It is the mark of an educated mind to rest satisfied with the degree of precision which the nature of the subject admits and not to seek exactness where only an approximation is possible." That translation itself is, of course, only an approximation and requires an appropriate degree of tolerance, but you get the idea.

Looking back a few decades, it is clear that the challenge in terms of tolerance and dimensioning shifted with the move from analog to digital measurements, and electrically there is the beginning of a second shift where highspeed digital systems blur back into the analog realm.

#### **TOLERANT OF TOLERANCE?** continues

Figure 1: Misunderstanding tolerance can lead to disappointment.

Those of us in the industry for long enough can recall the move from analog voltmeters to digital and from vernier scale to digitally encoded micrometers and calipers. Digressing slightly, I recall a very analog moment when, as a naïve 11-year-old, I and a school friend decided to measure the current available from mains electricity—with an analog AVO meter (safety note: not a wise move!).

The result was a large blue flash, melted meter cables and a visit from the local electricity authority as we had vaporised the main fuse in the supply box. Fortunately, we are both still here, and I still use a trusty old analog AVO meter for electrical jobs around the house. Perhaps that's why I ended up with a career in the electronics industry, but I have to say it's not as exciting as that first experience, and maybe that's not a bad thing.

Back to tolerance. In a supply chain, problems set in when tolerances are set incorrectly or when the tolerance specified is unachievable. The story in the PCB industry dates back to the introduction of CAM and the ability to set hole tolerances far tighter than those achievable with the available drills or drilling machines. It is important that everyone in the supply chain understands what is achievable and what is not. The same is true for electrical measurement. It also comes as no surprise that a long, complex supply chain also has a lot to take on board as

each particular measurement can present individual challenges.

Take electrical measurements: I have described how the nature of electrical measurement changes as frequency increases. The same is true for tolerance. When measuring at low frequencies, current, voltage and resistance are all capable of being measured with a high degree of precision with many decimal places of accuracy and tolerance on measurements can be tight indeed. But as the frequency starts to creep up it becomes harder to hold to such tight tolerances. At DC, tenths or hundreds of an ohm present little problem; but at mid frequencies, say, from 100MHz to 2GHz, then measurement of impedance presents more of a challenge. Perhaps a tolerance of 0.2 or 0.5 ohm is the best you can expect, and that depends on the impedance measured. Even the precision impedance air lines made traceable via NIST or NPL can present the user with a surprising amount of impedance uncertainty, limiting the achievable tolerance and absolute accuracy of measurement systems.

At even higher frequencies, resistance, voltage and current become even more tricky to measure, and RF engineers resort to power measurement, where the heating effect of the RF power is really the only way of measuring the gain or attenuation of a system, the voltages and currents being too elusive to measure.

Some systems are very

repeatable and sit

well within their factory

specifications, but the

specifications are there

for a reason; do not

assume because your

measurements are very

repeatable that they are

more accurate than the

published tolerance of the

measurement system.

#### **TOLERANT OF TOLERANCE?** continues

This is why you will see, as designers push high speed digital to ever loftier transmission speeds, that insertion loss S21 or differential insertion loss Sdd21 is measured as a ratio of power into the line under test vs power out. The difference between the power in and out will be the insertion loss. Putting a tolerance on this type of measurement is tricky as the measurement of the loss will depend as much on the design of the test pieces as on the metrology instrument.

It is interesting to look at this from a distance as, to a casual observer, accurate lowfrequency measurements need a good meter, but the probes can be quite simple and low in cost. As the frequency ramps up, shielding is often required, along with coaxial or transmission line probes. Additionally, the interconnect between the probe and the measurement system becomes a critical part of ensuring accuracy and repeatable measurements. At the highest frequencies, where ultimately a user may resort to a probe station, the probing system cost can be of a similar order to that of the measur-

ing instrument. In fact, at high frequencies, all the parts of the measurement system need to be carefully crafted to ensure you can make accurate measurements within the desired tolerance; typically, the higher the frequency, the more the achievable tolerance widens out.

It is interesting to look at some VNA specifications regarding tolerance and accuracy: you will find that the measurement precision depends on a blend of factors, including the design of the test piece. For example, if a coupon is designed with a very high loss (almost complete signal attenuation) or very low loss (almost 100% transmission), it is hard to make an accurate measurement of loss per unit length. Samples therefore need to be designed with an appropriate loss depending on the base material used. Therefore, for low loss materials the coupons may need to be longer (loss is proportional to line length) than for a standard loss FR4 material.

# What increases your production tolerance?

First—and, seemingly, one that people miss—you need to allow for the tolerance of your measurement system. Some systems are very repeatable and sit well within their factory specifications, but the specifications are

there for a reason; do not assume because your measurements are

very repeatable that they are more accurate than the published tolerance of the measurement system. Given that you have accepted this and you are working within the limits of your measurement system, let's take a look at controlled impedance traces and the possible offenders which may cause some of your products to fall outside, or close to, their permitted tolerance. Cross-sections are important here. The primary drivers of impedance are dielectric separation and trace width. Trace thickness and dielectric constant are second-order effects. It

follows then that variations in line width may cause traces to vary in their measured impedance. Taking several cross-sections can confirm if this is the case. As line width reduces, it becomes more difficult to achieve a given level of tolerance.

Surprisingly (to some designers, at least), the same is true for dielectric separation. The board thickness does vary in different parts of the PCB—copper density is a key driver of this—and it is essential to ensure the density of Cu is well balanced to ensure there are not excessive variations of height and therefore dielectric separation. Local variation of dielectric constant can also have an effect—witness the many papers on fiber weave mitigation—though, interestingly, low-twist fibres and mechanically spread glass can help this and perhaps in future the advances in glass design will reduce the need to deal with fiber weave variations in E.

#### **TOLERANT OF TOLERANCE?** continues

It is interesting that spread glass is one of those rare win-win coincidences as it was originally developed to ease controlled-depth laser drilling, the resin being far easier to ablate than the glass. A side effect of the improved cloth is reduced regional variation in E<sub>r</sub>. There is a third win here which no one saw coming: At very high (GHz) frequencies, the periodic variation in E<sub>r</sub> caused by weave mitigation can cause high-frequency variation in the insertion loss characteristics, but that's for another article.

# Summary

So, when specifying any measurement, you should ensure that the design authority (or supply chain procurement management) specifies realistically: that means both measuring within the limits of the capability of your measurement systems and recognising that in some cases an appropriate sample measurement test vehicle (coupon or sample material) is an important part of the measurement system.

Finally, the key to keeping tolerance as tight

as economically possible is an understanding of the materials and processes that are the key drivers of the property you are measuring. And if you are still wondering if the AVO survived its traumatic measurement experience, well, yes, it did. PCBDESIGN

#### References

1. A Designer's Guide to PCB Tolerancing, Polar Instruments Application note AP521.

Martyn Gaudion, CEO of Polar Instruments Ltd., began his career at Tektronix in the early 1980s. He joined Polar Instruments Ltd. in 1990 and was appointed CEO in 2010. Gaudion

also writes occasional articles for a number of PCB industry publications and regularly contributes to IPC high-speed, high-frequency standards development activities. To contact Gaudion click here.

# video interview

# Mark and Kelly on Value-Added Vendor Visits

by Real Time with... PCBDesign007

Guest Editors Kelly Dack and Mark Thompson have a lively discussion about the often underestimated value of keeping in touch with your suppliers through on-site visits.

realtimewith.com

# We are Commited to Delivering Outstanding Quality and Service, On-Time our CUSTOMERS AGREE!

Prototron Team,

Technology Kitchen develops microcontroller solutions for customers in many industries. Prototypes are a key piece to our phased development process.

We have appreciated the timely responses to our requests for quotes for various quantity, delivery and board finish scenarios. The Prototron team always hits the delivery date with quality boards! We have also appreciated your willingness to drop ship to various Technology Kitchen partners.

Everyone we interact with at Prototron makes Technology Kitchen feel like we are your only customer!

Thanks,

Ken Ward, Technology Kitchen

Click to Learn More

www.prototron.com

# Welcome to the 2014 IPC APEX EXPO how Guide

CONFERENCE & EXHIBITION March 25-27, 2014 MEETINGS & EDUCATION March 23-27, 2014 Mandalay Bay Resort & Convention Center Las Vegas, Nevada

This year, the Mandalay Bay Hotel and Convention Center is the site for the industry's premier event, featuring 430 exhibitors from more than 50 countries. Featuring advanced and emerging technologies in printed board design and manufacturing, electronics assembly, test and printed electronics, APEX is a great place to find new suppliers with new solutions and connect with colleagues from around the world. Plenty of free offerings are on hand—follow these links for a complete online show brochure or event schedule.

Here are a few highlights of what attendees may expect include:

- 430 exhibitors showing equipment, materials and services for printed boards and electronics manufacturing—plus printed electronics! There's no better place to see and compare.

- The <u>largest technical conference</u> for our industry in the world. Highly selective, the conference presents new research and innovations from experts in the fields of electronics assembly, test and board fabrication and design.

- FREE! Industry poster sessions—Catch up on the latest research and meet the authors.

- Professional development courses provide comprehensive updates on pressing industry concerns.

- Standards development meetings that help shape the future of our industry.

- IPC International Hand Soldering Grand Championship—Compete in or watch the excitement on the show floor.

- Other happenings on the show floor include the Show Floor Welcome Reception on Tuesday and a display of cutting-edge products and services in the New Product Corridor. There are also plenty of informational resources at the IPC Bookstore.

- Networking opportunities including an International Reception, First-Timers' Welcome, IPC Tech Talk, Women in Electronics Networking Meeting, and IPC Government Relations Committee Open Forum allow attendees to meet colleagues, get updates on key issues and share ideas.

To register to attend IPC APEX EXPO 2014, click here.

For an inside look at the show and in-depth interviews with industry insiders directly from the show floor, be sure to visit I-Connect007's Real Time With... site during the show. We're the only publication posting interviews and events in real time!

# Free Keynote Addresses All Three Days!

**Opening Keynote Address:** Tuesday, March 25, 2014 8:30-9:30 a.m.

# Peter Diamandis, M.D. Creating a World of **Abundance**

Through his work as chairman and cofounder of Singularity University and chairman/CEO of X PRIZE, Diamandis has proven the transformational power that exponentially growing technology has on companies, governments and humanity—and on "do-it-yourself" technologists and small companies who can now achieve what only governments or large corporations could do before.

# **Day Two Keynote Address:** Wednesday, March 26, 2014 9-10:00 a.m.

# **James McLurkin** Swarm Robotics and the Toys, Movies and Insects that Made it all Possible

They will flock. They will swarm. And they will tackle the dangerous, dirty and dull jobs for which humans are inherently ill-suited. They're multirobot systems—and one day they will become the norm, according to roboticist, inventor, researcher and teacher, James McLurkin. Inspired by the complex group behaviors found in ants, bees, wasps and termites, McLurkin's work focuses on developing software and programming techniques for groups of autonomous robots with populations ranging from 10 to 10,000.

As a child, McLurkin was constantly playing with Star Wars® toys and building with LEGO® bricks, cardboard boxes and any other materials he could access. Today, armed with degrees in electrical engineering and computer science from M.I.T. and University of California, Berkeley, McLurkin continues to harness his inventiveness to develop the robot swarms that will one day perform jobs ranging from warehouse operations to search-and-rescue missions to Mars exploration. Don't miss this fascinating look at the future of robotics and the technology that is making it happen.

# Day Three Keynote Address: Thursday, March 27, 2014 9-10:00 a.m.

# Diandra Leslie-Pelecky, Ph.D. The Physics of NASCAR

In a presentation based on her book, "The Physics of NASCAR," physicist and researcher Diandra Leslie-Pelecky, Ph.D., will take you behind the scenes of America's most popular spectator sport—and explain the feats of engineering that make NASCAR work. Drawing on her extensive access to NASCAR race shops, drivers, crew chiefs, engine builders and pit crews, Dr. Leslie-Pelecky will trace the lifecycle of a racecar, from its creation at leading race shops to competing in the action of the NAS-CAR series.

# IPC APEX EXPO

## Free IPC APEX EXPO BUZZ sessions

Eight free **BUZZ** sessions will be offered at IPC APEX EXPO this year. The industry's top technical experts on subjects ranging from automotive and new technologies to conflict minerals, export controls and technology roadmaps will provide insights into timely issues. Admission to the BUZZ sessions and the exhibit hall is free to pre-registrants, a savings of \$25 on-site. Click the link above for BUZZ session times and a complete schedule.

This year's BUZZ session topics:

- Underwriters Laboratories: Updates

- Advanced Fabrication Instruction Exchange Between Design and Manufacturing: The IPC-2581B Model

- Promoting Excellence: New IPC Standards for Reliability and Quality, and IPC Validation Services Program

- Forbidden by the Government: Electronics' Materials Restrictions

- INEMI Sustainability Forum

- Counterfeit Components

- •What's Coming in 2015 in Electronic **Technology Roadmaps**

# IPC PCB Supply Chain Leadership Meeting

# Monday, March 24 8:00 a.m.-5:00 p.m. (includes networking breakfast, lunch and dinner)

A learning and networking forum exclusively for senior-level executives of PCB fabricators and their suppliers, this meeting focuses on issues related to executive decision making in the industry, such as market trends, customer requirements and the economy. Hear from noted industry experts and find out how your peers are addressing common challenges. To view the full agenda, click here.

# IPC APEX EXPO 2014 Technical Conference

The IPC APEX EXPO technical conference is known worldwide as one of the finest and most selective in the world. Learn about new research and innovations from key industry players in the areas of board fabrication and design and electronics assembly.

Sign up for one day, the full conference or an All-Access Pass. Click here for complete registration information and forms.

WE'LL KEEP YOU MOVING | With Mentor Graphics® Valor™ Lean NPI Flow, New Product Introduction (NPI) engineering teams can discover a new level of integration between PCB design, manufacturing, and assembly operations. Mentor Graphics provides a unique, lean NPI flow solution, using industry standard ODB++ files to link between product models and manufacturing process definition, ready to use by shop-floor tools for programming and documentation. To maximize your overall NPI operation and to learn more click here.

# **Professional Development Courses**

# Sunday and Monday, March 23-24 Thursday, March 27

This year, 29 professional development courses are being offered, with each three-hour course focusing on a critical issue within nine specialized areas, including: assembly processes for lead free and tin-lead soldering; cleaning, coating and contamination; design; emerging technologies; environmental issues and compliance; PCB fabrication and materials; printed electronics; quality, reliability and test; and supply chain/business issues. Course attendees will receive an instructional handbook to reinforce key information and use as a reference when they return to work.

Among the instructors leading the courses are Rainer Thueringer, Ph.D., Technische Hoch-

schule Mittelhessen; S. Manian Ramkumar, Ph.D., Rochester Institute of Technology; Phil Zarrow, ITM Consulting Inc.; Jennie Hwang, Ph.D., Sc.D., H-Technologies Group; Ray Prasad, Ray Prasad Consultancy Group; Gerjan Diepstraten, Vitronics Soltec; and Mike Bixenman, DBA, Kyzen.

Click here for a complete list of professional development courses and instructors.

# The PCB List—Find out what it's all about in the I-Connect007 booth!

Brought to you by PCB007, The PCB List is the world's most comprehensive online directory of printed circuit manufacturers, anywhere. Buyers, specifiers, designers and others looking for a PCB fabricator will appreciate the intuitive navigation, detailed search capability, and global reach of The PCB List. With a Showcase listing, a PCB fabricator can create a neat, organized presentation that puts all pertinent information at a potential customer's fingertips.

Drop by the I-Connect007 booth to see for yourself how easy it is to find a fabricator, or create a Showcase listing!

# Real Time with... **Interviews and Panel Discussions**

This year, I-Connect007 and the Real Time with... program returns to Las Vegas, Nevada to bring you complete video coverage of IPC APEX EXPO 2014. Last year, we brought you more than 150 interviews—and this year promises to be just as prolific.

The Real Time with... team of editors, guest and videographers will be working throughout this seminal event to capture the keynotes and bring you one-on-one interviews and panel discussions with the industry's top technologists, engineers, and business leaders as it happens!

Visit Real Time with... for updated information about IPC APEX EXPO 2014.

# The Absolute Best Value in High Technology Printed Circuit Boards

Since 1971, Eagle Electronics Inc. has provided our Customers with the highest quality Printed Circuit Boards at fair and competitive prices. We are committed to exceeding our Customers' expectations and requirements, acheiving total customer satisfaction on each and every job. It's just the way we do business!

With Eagle, you can expect:

- Rapid Response to Quote Requests

- Fair and Competitive Pricing/Costs

- 100% Quality Performance

- 100% On-Time Delivery Performance

- Flexibility Scheduling

- Stock/Consigned Inventory Programs

- Thorough follow-up after job completion

- Total Satisfaction!

click here for more reasons why you should use eagle!

www.eagle-elec.com

# **Differential Education 101** for PCB Designers

by Dan Smith **RAYTHEON MISSILE SYSTEMS**

What is the state of PCB designer education in 2014 and where is it going? Where should it be going? My new column will focus on PCB design, design processes, education and a host of topics that are important to PCB designers.

As such, I would like to hear from PCB designers and their managers about where their minds and dollars are headed regarding staying at the head of our industry.

Let's get started! Solve this equation:

The average time to solve this is three minutes. For those of you who remember differential equations, have fun. For the rest of you who are resolved not to attempt this problem and are now feeling your blood pressure going down, I would like to explore the state of formal and informal PCB designer education.

Before I attack the problem in this new column, I am dividing my thanks (historically) to four distinct groups of formal and informal educators in the PCB educator community.

First, I'd like to thank all of the PCB design educators who have tirelessly taught around the globe and written articles and books to offer their insights. For those who are unfamiliar with the educator's rule of "class preparation time," as a minimum, one minute of class lecture or lab requires a minimum of five hours of research and preparation. If the assembled students ever cared to realize why many teachers look tired but feel enthusiastic during these formal courses, it is because these same educators live for the "Aha!" moment of joy they see on their students' faces. There is no dollar amount that can equal this moment that educators live to see.

Second, a big thank you goes to those who have participated in industry and companyspecific design standards and practices. These participants collectively put in the range of in-

# Cut your PCB design time

Step up to CADSTAR - Start your trial today

#### Advanced 45-degree routing and pushing

The ultimate in speed and precision for manual routing, the **Activ-45** router provides single-click "follow me" routing with automatic completion, using push-aside, springback and segment break options to tackle even the most complex layout challenges.

#### Be a "Smart designer" - Download the CADSTAR App

**CADSTAR Touch** is a free PCB design productivity App that allows remote control of CADSTAR's view and program functions.

- Pan

- Zoom

- View all

- Run Macros

- More...

#### **CADSTAR** includes:

- Schematics

- Constraint Browser

- Placement Planner

- High-speed routing

- Signal Integrity

- Power Integrity

- EMC

- 3D Mechanical verification.

CADSTAR - Proven expert desktop PCB design solution

www.zuken.com/cadstar-trial

Westford, MA, USA

Tel: 888 332 7227

#### **DIFFERENTIAL EDUCATION 101 FOR PCB DESIGNERS** continues

finite man-hours, just to get their thoughts on paper so that others can grow their skill sets exponentially. This same participating group gets inversely proportional amounts recognition, usually little or none.

Third, to all of the EDA tool vendors, thank you for showing us how to use these tools so that we can become more productive. They have taken a wide variety of ideas, equations, and other theories, and synthesized them to formulate tools that have subtracted hours, weeks and months from design schedules. All the while, these companies have helped us understand and master the additions of newer design concepts, such as highspeed signals and HDI via stackups.

Lastly, we need to recognize that the majority of growth and education is actually indebted to the PCB design community itself, who have remained a positive force at seminars, webinars, and vendor fairs.

informal education If all four of these groups opportunities dried up. were put into the denominator, from any starting point in the past few decades, the numerators of the participation for each of these groups would slowly approach the absolute zero of Lord Kelvin.

Businesses (and society in general) prefer to align themselves with formal education (degrees, awards, and certificates) rather than informal education (i.e., the school of hard knocks), because it affirms that a person has participated in a structured environment and attended a minimum set of science-based foundational courses.

Yet it is the formal educational model that has never materialized for our industry.

Formal education provides the best foundation for growth as a subject matter expert, but education is also now a business. Yes, there are rankings of the top schools for each vocation, but it is also about the economics of providing a curriculum that will attract the most money from students, alumni, industry, and special interest groups.

> Informal education flourished when major companies' engineering teams actively participated with the manufacturing community. Side "special projects" of experimentation allowed for discoveries and inventions that created advancements in the PCB design process. But as interest and money was diverted away from these projects, informal education opportunities dried up.

The PCB design process has been stable for more than 20 years. The only significant PCB educational push in the past 10 years has focused on better understanding the physics of the newer devices and their interaction with the substrate interconnections.

When new PCB design articles are written, the most effective way to distribute this content is through the Internet. The weekly/monthly

distribution of these articles has caused me to take a step back and notice a significant education void that boils down to three high-level questions:

- 1. Why aren't these PCB design process articles being channeled into formal courses, lab experiments and textbooks?

- 2. Why hasn't there been an industry push to create a complete and consistent curriculum that could be taught by every technical college in the world?

- 3. Is the PCB user community content with the current education situation, or do they want more than what is being offered?

But as interest and

money was diverted

away from these projects,

#### **DIFFERENTIAL EDUCATION 101 FOR PCB DESIGNERS** continues

Instead of just reading more personal observations, it is far more productive for me to offer you, the PCB designers and managers, a chance to supply some of your thoughts by participating in an e-mail survey. Editor Andy Shaughnessy and I want to hear your collective voices, and we will publish the results for all to see.

Thank you for reading this column, and more importantly, thank you in advance for vour feedback.

To take this short survey on PCB design and design education, click here. Next month, we'll go over the results. See you next month! **PCBDESIGN**

Ed: This series on design education will continue for the next few months. Dan wants your feedback, so don't be shy. You may even see your name in an upcoming edition of "The Town Crier."

Daniel J. Smith is a principal technologist for Raytheon Missile Systems. He has taught multiple aspects of the PCB design process internationally, and he has authored several PCB-related

patents, articles, and standards over the past 30+ years. To contact him, click here.

### **Optical Circuits Flexing Their Way to the Forefront**

For futuristic applications like wearable body sensors and robotic skin, researchers need to ferry information along flexible routes. Electronics that bend and stretch have become possible in recent years, but similar work in the field of optics--communicating with light instead of electrons--has lagged behind.

Now a team of Belgian researchers reports progress on this front with what may be the first optical circuit that uses interconnections that are not only bendable, but also stretchable. These new interconnections, made of a rubbery trans-

parent material called PDMS (poly-dimethylsiloxane), quide light along their path even when stretched up to 30% and when bent around an object the diameter of a human finger.

Until now, the researchers say, no one had discovered a way to enable these materials to carry light while stretched. Past efforts also included embedding waveguides made of semi-rigid glass fibers into a stretchable substance. In the new method, the stretchable substance itself is the waveguide.

The new connector consists of two materials, both made of PDMS: a transparent core through which the light travels, surrounded by another transparent layer of PDMS with a lower refractive index, a characteristic of the material that describes how light moves through it.

Bending a waveguide beyond a certain point causes some of the light trapped in the core to escape, a process called optical loss. The Belgian team tested how far they could bend and stretch their new optical connector before too much light escaped.

"We were surprised that stretching had so

little influence on the waveguides and also that their mechanical performance was so good," Missinne said. The quide's reliability was also "remarkable," he said.

This work has been performed at the Centre for Microsystems Technology (CMST), a laboratory associated with imec and Ghent University.

# **Properly Designing PCB Footprints**

by Nicholaus Smith

INTEGRATED DEVICE TECHNOLOGY INC.

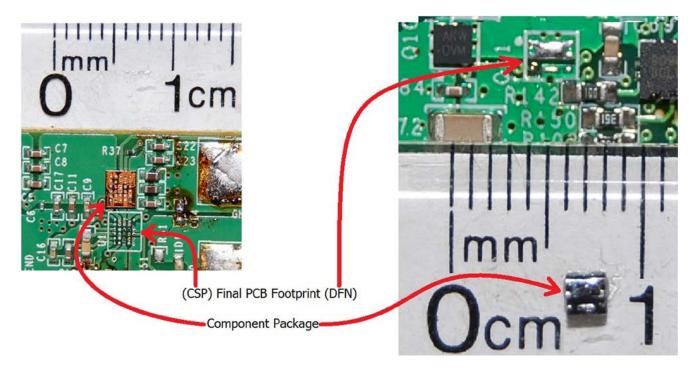

Today the geometries of board-level circuits are being driven to optimize space, cost, and performance, resulting in a large selection of fine-pitch components, connectors, and integrated circuits. Overcoming the challenges and the complexities of the circuit is challenging enough without considering the obstacles of mass producing the end-product with extremely high yield expectations.

Improperly defined PCB footprints are the culprits behind thousands of costly, time-consuming failure analysis investigations. For the sake of simplicity, it will be assumed that the circuit and all connections are schematically correct and any failures are the result of unreliable footprint designs assembled properly onto the PCB. The most common failures are caused

by solder shorts or open circuits that develop during assembly. Other potential defects include poorly contemplated pin escape routing, improper thermal design, and the dreaded intermittent failure.

It is imperative to implement PCB layouts with a strong understanding of the assembly process and how the PCB component footprint can influence yield and performance. This is especially important today, due to factors such as: (a) the expansion of integrated circuit product lines manufactured with pin pitches specified at 0.4 mm and below, and (b) the plethora of package variations available, such as chip scale packages (CSP) and quad flat packages (QFN) in double and single rows.

Prior to addressing footprint design techniques, we must define some layer definitions used in PCB manufacturing, and explain how these layers impact the final board. The pin will be identified as the actual solder contact point

# INTRODUCING COOLSPAN® TECA

thermally & electrically conductive adhesive

# Rogers can help by being your reliable conductive adhesive film source

Get the heat out of those high-power PCBs. COOLSPAN® Thermally & Electrically Conductive Adhesive (TECA) Films are ideal for dissipating heat in high-frequency circuits. COOLSPAN adhesives feature outstanding thermal conductivity (6 W/m/K) and reliable thermal stability. Keep things cool, with Rogers and COOLSPAN TECA film.

Visit Us At AP Booth #1828

www.rogerscorp.com

#### MEET YOUR COOLSPAN® **TECA FILM SUPPORT TEAM**

Leading the way in...

• Support • Service • Knowledge • Reputation

#### SCAN THE CODE TO GET OUR CONTACT INFO.

**Dale Doyle**

John Dobrick

Scott Kennedy

John Hendricks uropean Sales 1anager

Kent Yeung Regional Sales Director Asia

If you are unable to scan a VR code please visit our Support Team website at www.rogerscorp.com/coolspan

#### PROPERLY DESIGNING PCB FOOTPRINTS continues

that is used to mechanically and electrically connect the package to the PCB. Once the PCB has been etched, laminated, and the vias have been electroplated according to design, the next process step involves solder mask application to the outer surfaces of the PCB using printers, photo-masking, and radiation hardening. The role of the solder mask is to keep the solder on the pin during reflow. The solder paste is applied during assembly and is controlled by a layer called the paste mask.

Regarding the final PCB, all of these layers are geometric shapes that are drawn during footprint generation and are intended to facilitate connecting the pins of the device to the PCB. At this point the board would be blank with openings in the solder mask webbing at each pin. It would then be placed into a solder paste application machine where a 4-mil-thick stencil with laser-cut openings matching the pin etch is placed over the board, and then solder paste is applied by a squeegee sliding across the stencil, forcing solder paste onto each pin.

The stencil is then removed, leaving solder on the pins of each component. The solder paste is comprised of a slurry of flux and lead-free solder spheres, and it sticks to the PCB pins and not to the stencil due to the stickiness of the flux and surface tension. Finally, a pick-and-place machine puts each part in the defined locations and rotations; then the PCB is conveyed through a reflow oven. After assembly, the boards are tested and any failures are categorized; the root cause analysis is conducted assuming the percentage exceeds permissible yield limits.

Now a CSP will be considered and footprint design for high yield will be the focus. The most important aspects of any component are the pin geometries, pitch, and the package keepout. The pitch is the spacing from the center of a pin to the next adjacent pin. The keepout is the area defined around the component; it is intended to force the designer to provide sufficient clearance between components, so that they do not interfere with each other during placement and reflow.

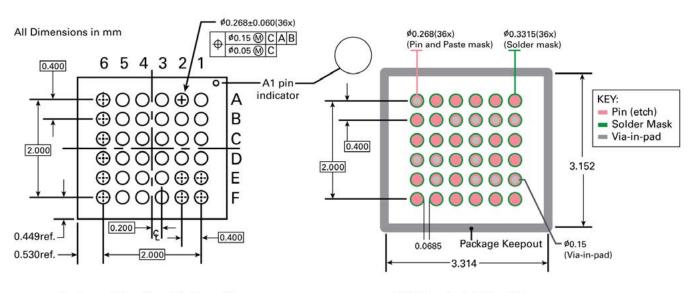

When designing the footprint for the package drawing shown in Figure 1 with a pitch of 0.4 mm, key factors will be:

- a) specifying the solder mask so that it is guaranteed to be applied in between each pin without overlapping any pins

- b) specifying the pin diameter for consistent even soldering

Package Drawing, Bottom View

**PCB Footprint, Top View**

Figure 1: 36-pin CSP packaging diagram used to hold an IDTP902x wireless power receiver IC.

Even if the pin does

get partially covered,

the risk is that the

electrical connection

could be reduced by

sidered.

#### **PROPERLY DESIGNING PCB FOOTPRINTS** continues

c) determining a via-in-pad that will allow for PCB manufacturers to reliably drill and plate the inner pins so they may be contacted using non-component side layers of the PCB

Most PCB manufacturers are able to apply solder mask down to 0.0635 mm (2.5 mils) and will guarantee that they can create a void in solder mask down to the same size. Therefore, to be certain every PCB will have solder mask applied between each pin while keeping the pins free from solder mask, it is recommended that at least 0.1905 mm of clearance is maintained in between each pin. This is equal to having two solder mask void widths (one for each pin) and one application width (gap between pins).

For this package, the ball up to 12% of the size is 0.268 mm + /- 0.06 mmwith a pitch of 0.4 mm that available pin area. leaves only 0.072 mm in between the pads if we design for the maximum possible diameter. This will leave insufficient separation for solder masking to be reliably applied; therefore it is not acceptable to design the pin diameter at 0.328 mm. Now faced with a tradeoff, the highest yield design option is to apply the necessary solder mask bridge between pins and sacrifice the solder mask void.

This tradeoff is valid because the diameter of the pin will be included in the solder mask free area which will allow for adequate registration of the void, while giving the PCB manufacturer the needed solder mask width for guaranteed application. By specifying the pin diameter at 0.268 mm and the solder mask void diameter at 0.3315 mm, this leaves 0.0685 mm for solder mask, which provides crucial extra width since insufficient solder mask will lead to solder shorts under the package. Solder shorts under such packages are impossible to repair without removing and replacing the IC, an operation with lower success rates than the original assembly, due to the complication of applying a single device in a congested area on a potentially suspect footprint. With these diameters,

the clearance from the solder mask to the pin is only half of the recommended clearance of 0.0635 mm; however, since the solder mask is not applied over the pin, that area is included in the void, thus the risk of having solder mask on the pin is reduced.

Even if the pin does get partially covered, the risk is that the electrical connection could be reduced by up to 12% of the available pin area. This compromise still leaves 88% guaranteed

contact area between the CSP pin and the PCB pin, thus allowing

> even PCBs created on the low end of the tolerance band to still function with most likely unnoticeable defects. Another complication with such a device is the need to use via-inpads to access the inner pins (rows B-F and columns 2-5) followed up by back-filling the vias so that the pins may be plated on the surface until they are flat and even with the

rest of the PCB copper. Typical vias require that the finished pad diameter is 0.127 mm wider than the finished plated hole diameter and the typical minimum via diameter without a surcharge is 0.127 mm-0.1524 mm. For the 0.268 mm pins requiring vias-in-pad, the solution is to avoid using the minimum via while still allowing for manufacturing tolerances, thus a 0.15 mm via is recommended, leaving only 0.059 mm of pad diameter for registration and drill tolerance. Once the hole is drilled, the

selection of the filling material should be con-

There are two types of back-filling material in use: conductive and non-conductive. Besides the obvious difference, it should be noted that even the conductive fill material conductivity does not approach that of copper (electrically or thermally) and most have expansion coefficients that are very different than the surrounding via wall. During temperature variations of the PCB, non-conductive fill more frequently stretches and cracks the thin via walls compared to its counter-part, causing a higher percentage of intermittent or permanent failures. On the

#### **PROPERLY DESIGNING PCB FOOTPRINTS** continues

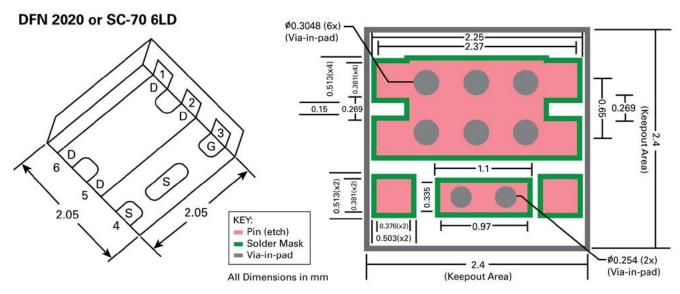

Figure 2: DFN 2x2 mm 6 LEAD (SC-70 6LD) single transistor package.